Other Parts Discussed in Thread: TINA-TI

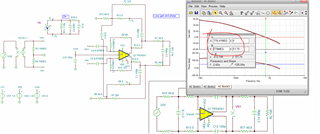

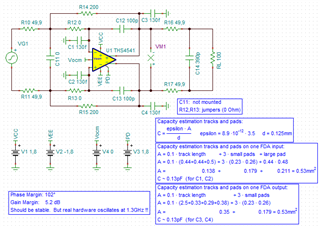

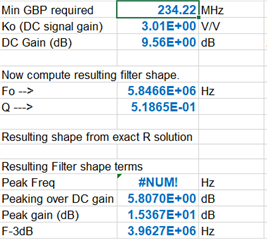

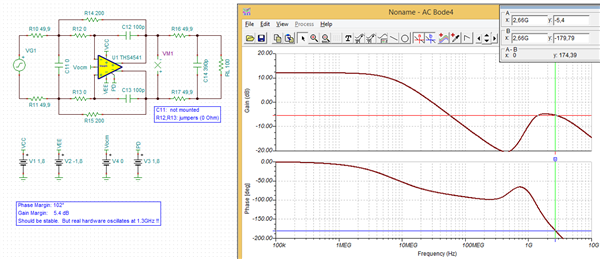

I have designed FDA in a low pass configuration like that:

But the real hardware is not stable. The amp is oscillating at 1.3GHz.

I have removed C14 (I skip the picture here), but the problem remains the same.

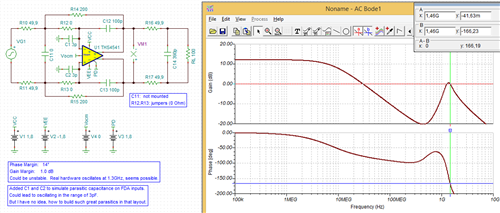

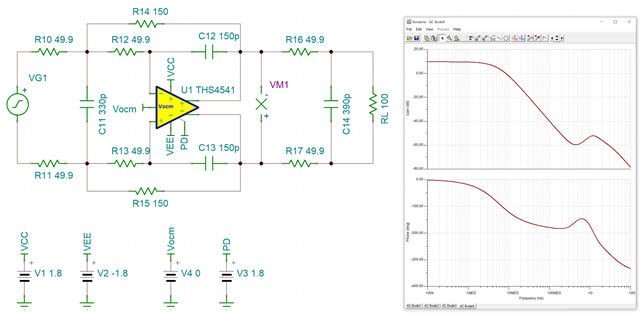

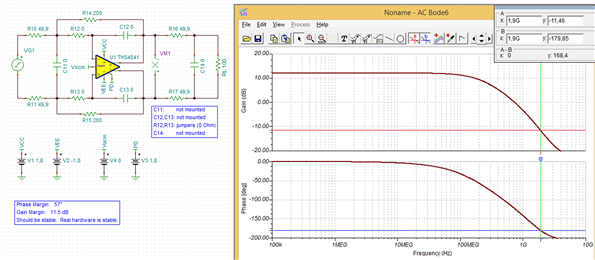

I have additionally removed C12 and C13 (now without the low pass) like that:

The real hardware (without the low pass) is stable now.

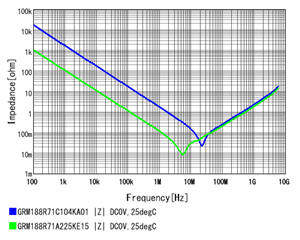

Can anyone tell me what I did wrong with the low pass?

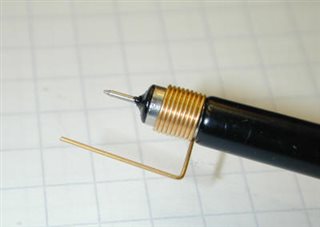

Of course, it could have to do with the layout. But first I wanted to know if I have a general error in the schematic.

Thanks