Other Parts Discussed in Thread: AMC1301-Q1, OPA1652

Hi, my name is Oliver, TI Korea Field Application Engineer.

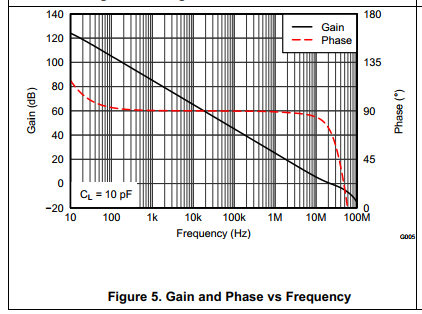

This is the part of OPA202 datasheet.

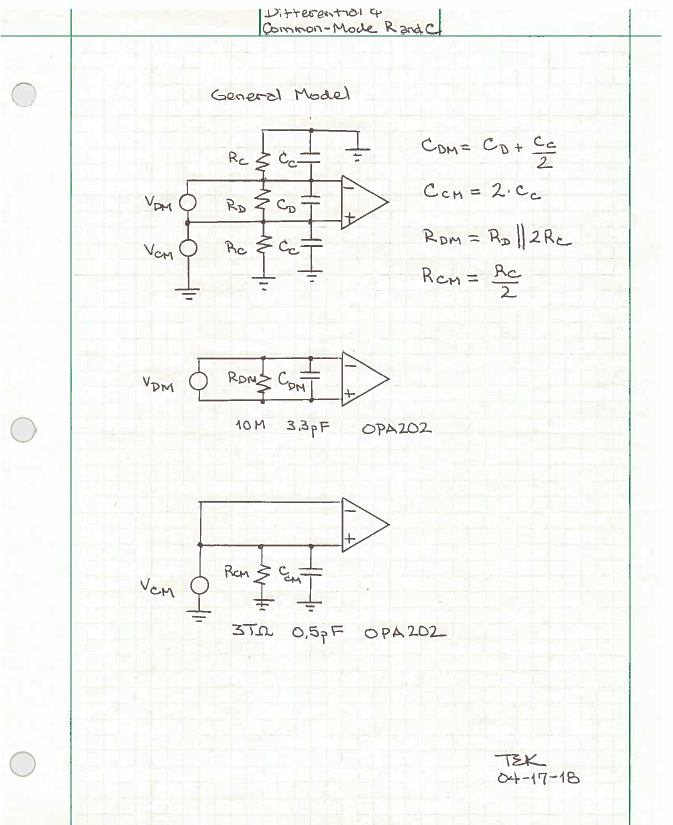

(1) I wonder why input capacitance? why not input impedance?

(2) What's the common-mode input capacitance(or impedance)? Is it different from the single-ended input capacitance(or impedance)?

(3) If they are different, is there any other reason why OPA202 datasheet doesn't have single-ended input capacitance(or impedance)?

For example, in case of AMC1301-Q1, there are differential input resistance and single-ended input resistance and not common mode resistance. I am confused too many terms are used in various datasheets.

I really want to hear your opinion about this.

Thank you.