Other Parts Discussed in Thread: SMV320C6727B-SP,

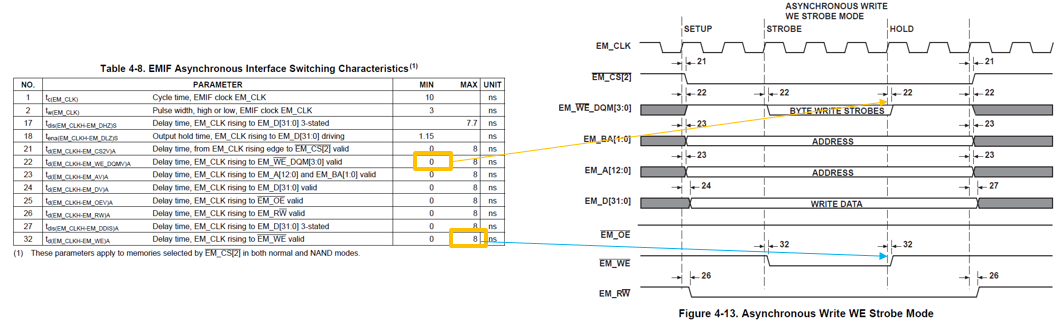

- The Asynchronous EMIF bus has the following delays from pg. 49 on the datasheet, with signals having a min of 0 nS and max of 8 nS. For the write hold timing if I consider the minimum delay for EM_CLK to EM_D being 0nS and maximum delay for EM_CLK rising to EM_WE being 8 nS I would have a negative hold margin considering the large difference between min and max. I’m wondering if my interpretation of this timing diagram is incorrect and that actually there’s two clock cycles of positive margin for hold before the Data delays are considered?

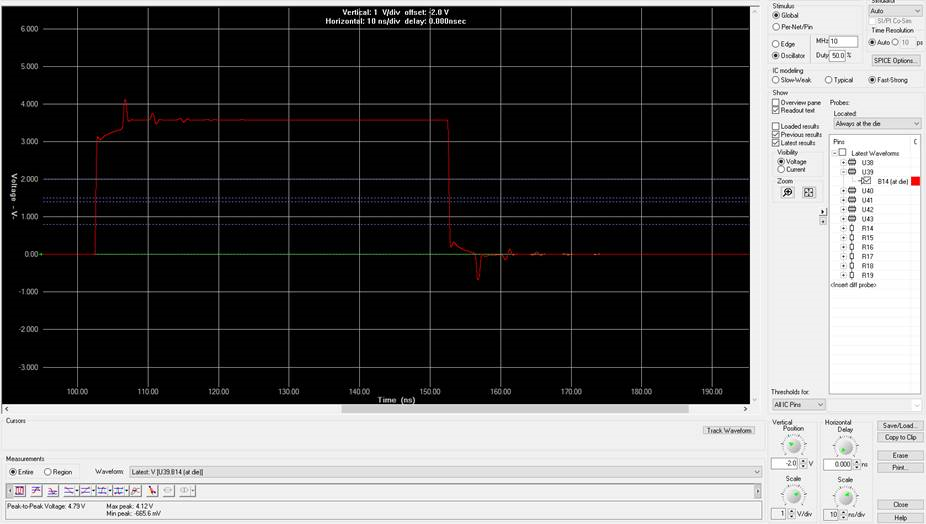

2. Looking at the waveform below I’m wondering if there’s an AC spec. that would be acceptable for exceeding the absolute Max/Min overshoot for the 3.3V digital I/O receivers. As shown below the peak to peak voltage is 4.12V to -0.666V, which exceeds the datasheet spec of -0.3 to DVdd + 0.5V. However the spike is only for brief period of time considering the period of the signal. Would this be acceptable for this device and is there documentation for that?