Other Parts Discussed in Thread: DRV3245Q-Q1

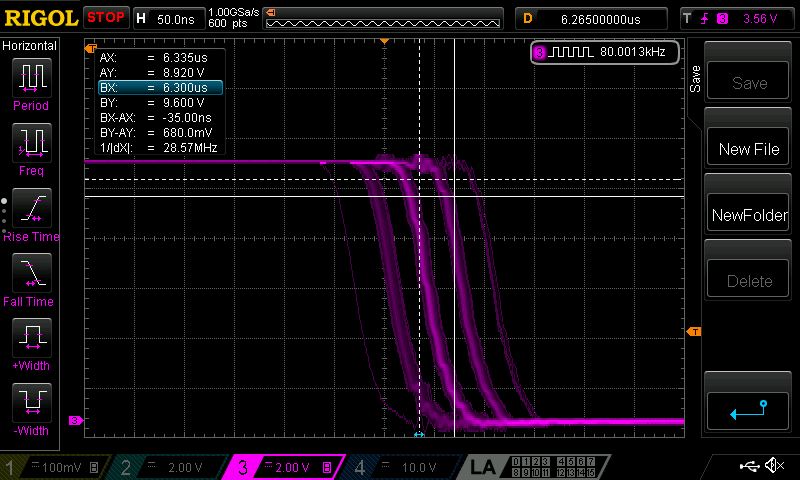

I'm struggling to understand what is going with the dead time in my circuit. I understand that the DRV8305 tdrive system automatically ensures that a switch is turned off prior to turning on the opposite transistor. This is a great feature in concept; however I am concerned that the dead-time that it inserts is not consistent, and varies by 40nS between switching cycles.

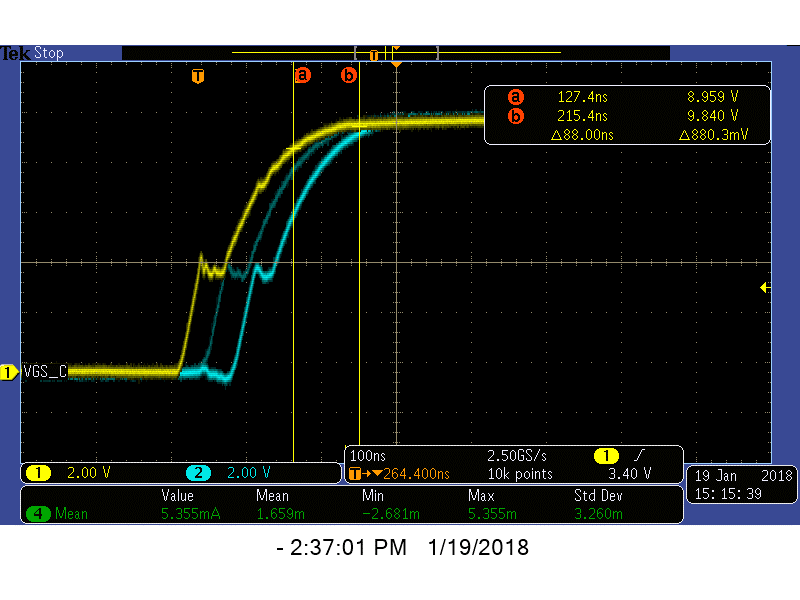

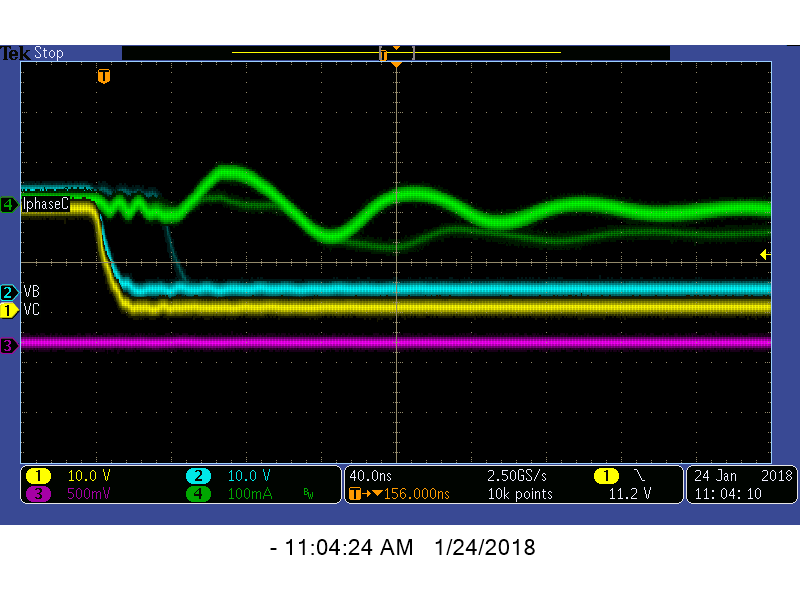

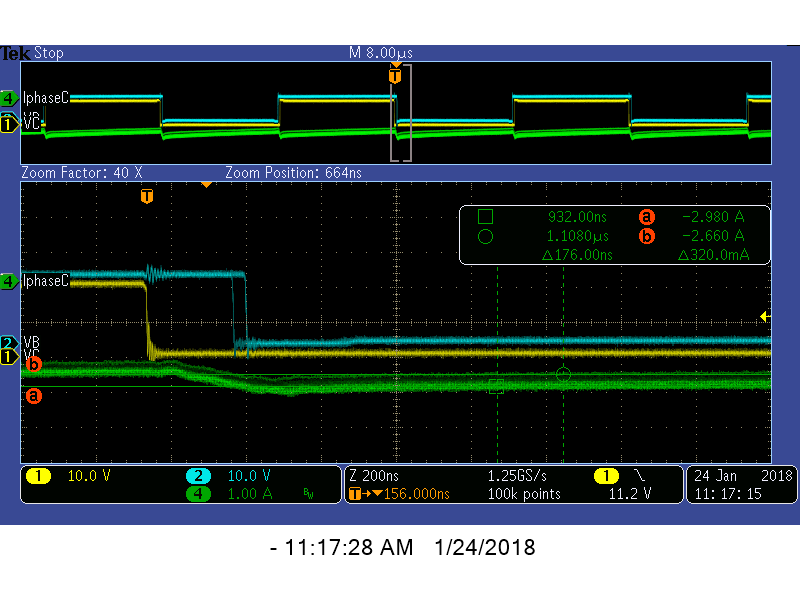

I've got my processor outputting constant pwm, and when I look at the low side there is a consistent relationship between the gate commands (see second scope trace), however when I look at the actual gate commands coming out of the DRV8305, I see inconsistency. Below is a scope shot of that; Yellow trace is phase B lower switch gate. Blue trace is phase C lower switch gate. Current is flowing, but small, pwms are in a fixed state. You can see that the blue trace is going high either 40 or 80ns after the yellow trace (the trigger)

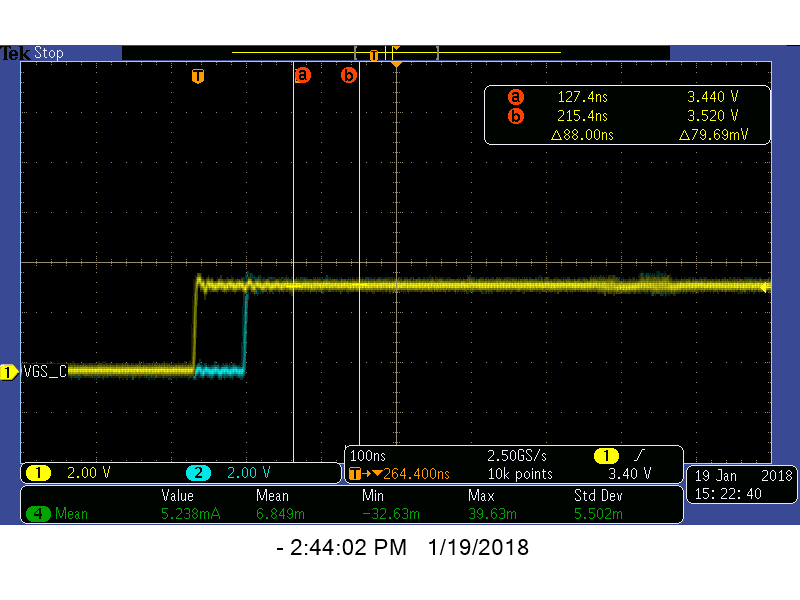

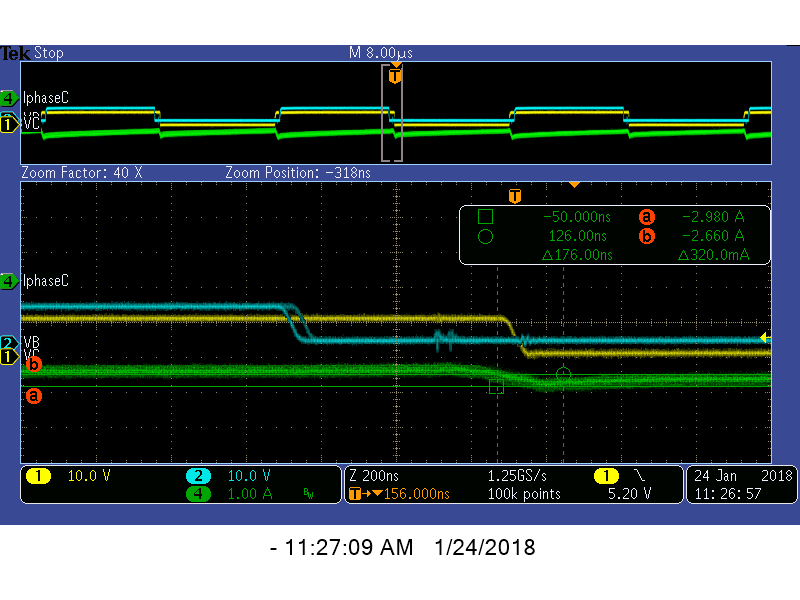

This plot below shows the same signals at the input to the chip - no variation visible.

I'm running a very low inductance motor, so when the motor is stopped, as it is in this test, the duty cycles are small. The variation that is being created by the dead-time inconsistency has a large impact on current, and causes instability. I'd like to make it go away. Is there some way to turn off dead time on the DRV8305? Then I will generate deterministic 100uS dead-time on my microcontroller. If there is not way to turn it off, what steps can I take to stabilize this effect?

Thanks