Hi,team

We use your EVM board which can work well in slave or master TDM.

But now factory has produced formal boards.

There is hardware difference:

1)EVM some power is use 3.3v like AVDD,but our board all power use 1.8v

2)EVM use analog MIC,and we use 8 DMIC.

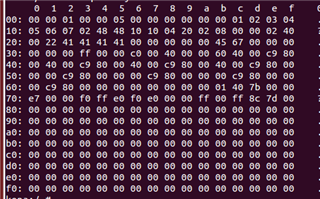

According to the document tlv320adc3140.pdf, i config following regs:

slave mode:

0x02 0x01 // power

0x3c 0x40 //mic setting

0x41 0x40

0x46 0x40

0x4b 0x40

0x22 0x41 //GPO setting

0x23 0x41

0x24 0x41

0x25 0x41

0x41 0x48 // default 48K 12.288M

0x2b 0x45 //GPi setting

0x2c 0x67

0x73 0xff

0x74 0xff

0x75 0x60

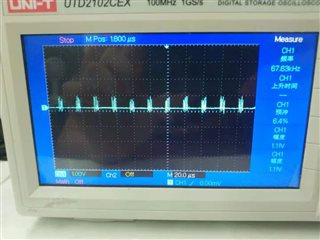

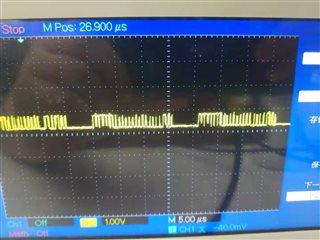

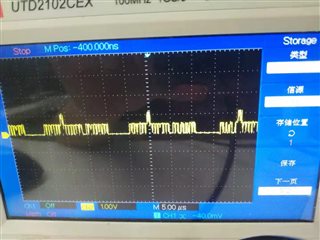

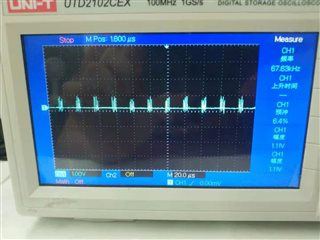

Now the DMIC can get 3M CLK and output data.

But record data is NULL,i think ADC output data have problem.

ADC maybe output null data.

Please help check it.

thanks