Other Parts Discussed in Thread: TAS2505

Hi, TI Support Team

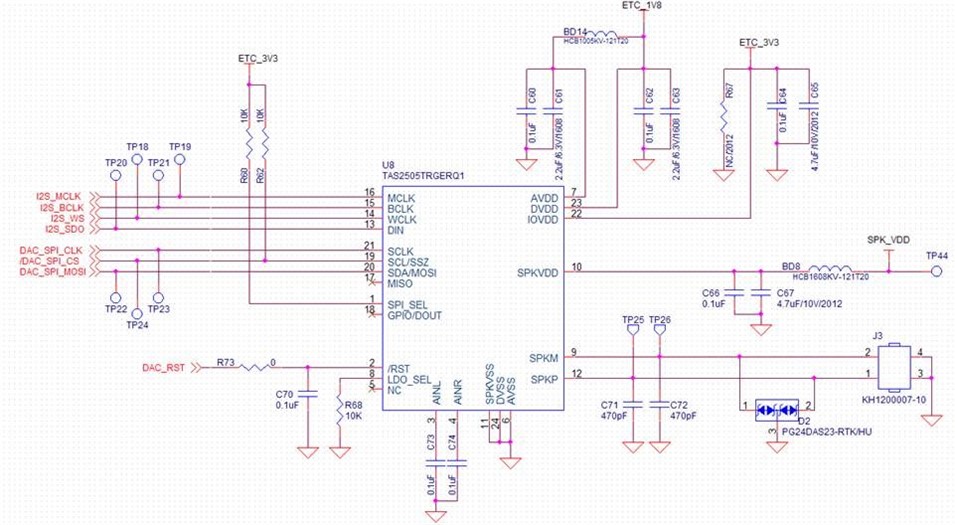

A customer is reviewing a design using the TAS2505TRGERQ1.

Please check the inquiries below.

1. Is it correct to connect the IOVDD (22th pin) pin to 3.3V to set the MCU and SPI interface to 3.3V?

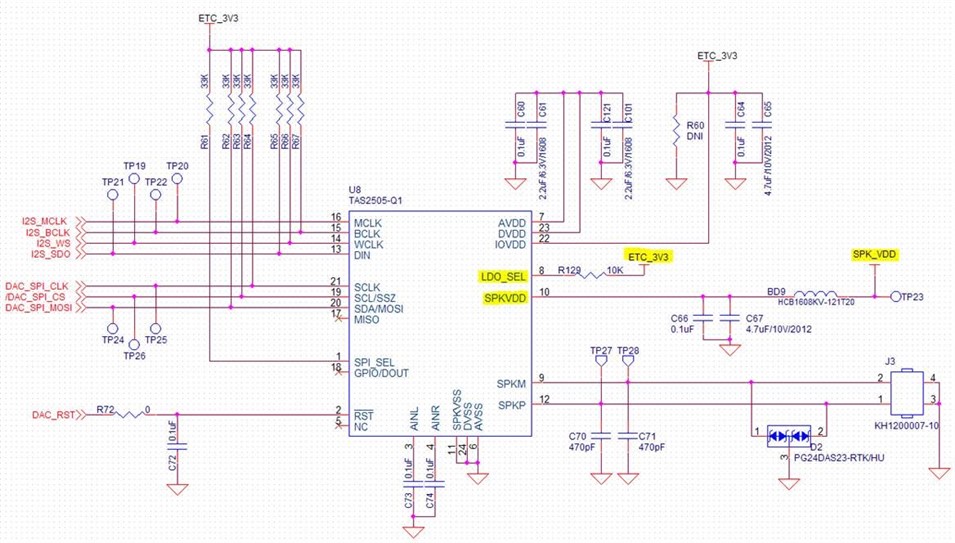

2. You want to use an internal LDO.

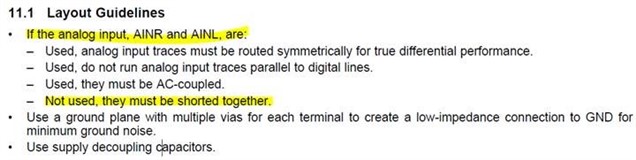

Connecting the LDO_SEL pin to SPKVDD is specified in the datasheet.

Is there any problem with the circuit configuration as shown below?

- I want to control ON/OFF of 5V supplied to SPKVDD using FET switch. (to remove speaker output noise)

- Because of the above configuration, when the LDO_SEL pin is connected to SPKVDD, 5V is not normally supplied, but only when the voice is output. (Refer to the circuit below)

- Is it okay to connect the LDO_SEL pin to an external 3.3V?

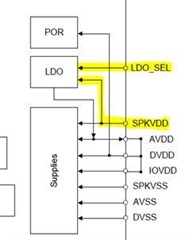

3. Looking at the datasheet block diagram, is LDO_SEL the ON/OFF signal and the POWER SOURCE of LDO is SPKVDD?

Please confirm the above inquiries.

Thanks.

Regards,

MJ