Hello Guys,

Good day.

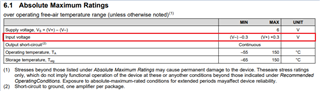

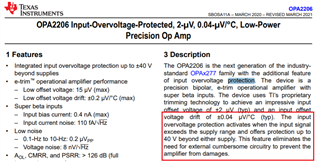

Our customer wanted to know what is the maximum voltage the non-inverting input of this part can withstand without being powered? He's using this opamp for a buffering circuit in his design to measure battery voltage. So the non-inverting input could see 0-1.6v DC before the opamp is powered up by the system.

Thanks and regards,

Art