Hi,

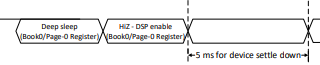

On rare occasions(about once per 200 times power on sequence), TAS5825P does not work correctly.(CLK_FAULT)

I2C communication seems to be working correctly.(Read/Write)

But no sound after initialized.

In NG state, CLK FAULT flag in GLOBAL_FAULT1 register is activated.

And,

- FS bit in FS MON Register is set to 4'b0000.(Usually set to other suitable FS).

- Bit 3 in CLKDET_STATUS Register is set to 1.(Usually set to 0)

- POWER_STATE Register is set to 0x02.(Usually set to 0x03)

Once call initialize function again in NG state, TAS5825 works correctly.

Question

1. What is the cause of CLK FAULT?

2. How can I recover from this fault state without PDN?

If you need more information, please let me know.