Team,

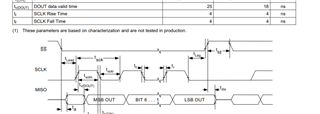

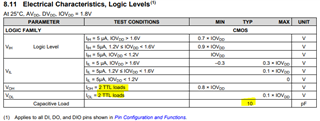

I’m working on a design using the TI TLV320AIC3204IRHBT CODEC and I’ve got a scenario where I have 6 CODECS on the same SPI bus with an FPGA as a bus master. I am trying to understand what sort of capacitive load the CODECs impose and can drive on their digital IOs. It looks like they have a 10pF input capacitance, but it’s unclear what they can reliably drive on a 10MHz SPI bus:

The “2 TTL loads” is the test condition. In my case I have 6 CODECs (10pF each) and the FPGA (4pF) on the MISO line, so ~64pF total. Would I be wrong to interpret the above data table to imply the CODEC IOs can drive 20pF?

Thanks for any further information on this part.