Hi team

I would like to ask a question about PCM6340 clock frequency.

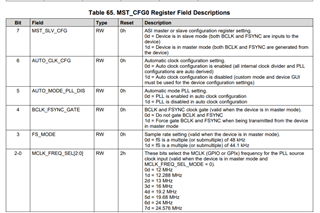

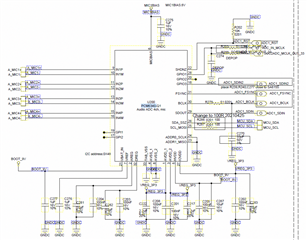

Customer expects to use the internal clock of the device, PIN28 GPIO1 has np MCLK input; but after the configuration is completed, the frequency of PIN31 FSYNC customer measured is different from the configured frequency; modify the register configuration according to the datasheet, the output frequency is still different from the value on the datasheet.

Here is their configuration both hardware part and software part:

Schematic:

Initial register configuration:

PCM6340 init .xlsx

Test Results:

1. Address0x14: If FS_RATE is configured as 48kHz, the actual measurement is 14.7kHz; if configured as 16kHz, the actual measurement is 4.86 kHz.

2. Connect a 12.288MHz crystal oscillator to GPIO1, the actual measured PIN31 FSYNC frequency is the same as the configured frequency.

Could you please help analyze whether there is a problem with our design and how to modify it to accurately output the clock? Thank you.