hi audio team,

I have few questions about TPA3255.

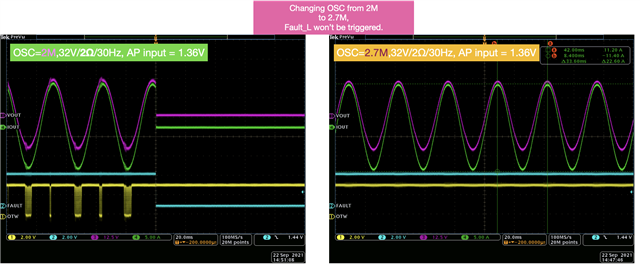

Q1: The experiment config is PBTL mode with 2ohm pure resistance loading. Using external clk (2M) and PVDD is set to 32V;

when checking the switching performance, the input signal frequency(sent out from AP) is 30Hz, Fault _L signal will be triggered when input voltage is at range 1.27V-1.45V. except the below range, tpa3255 can work normally. Pretty weird.

But there's two way to solving this issue while I cannot explain the reason. first is to increase PVDD voltage. then under same condition, fault l won't be triggered to LOW.

second way is to increase the OSC clk(to around 2.7M), fault_l will not be triggered to low.

can you help to explain why these two solutions have here? especially is there any requirement on external clk value selection?

Q2:

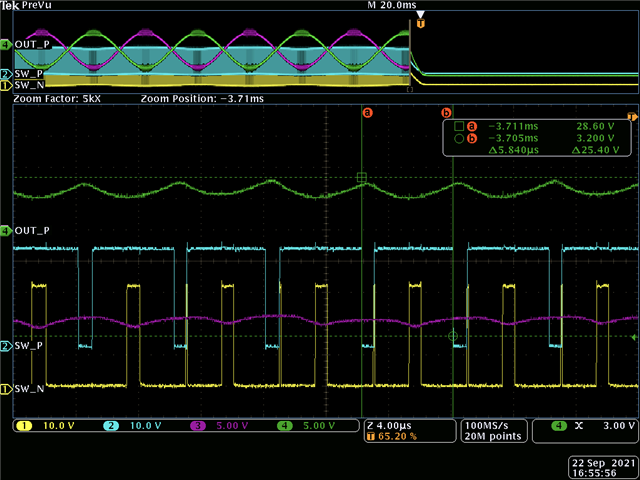

when clipping protection is triggered. narrow wide pulse can be found and sw-p and sw-n have lots of overlap here.

is it normal??