Hi Sir,

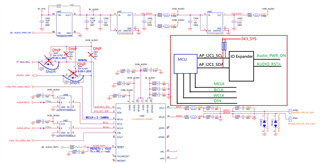

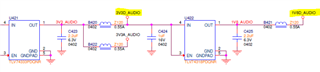

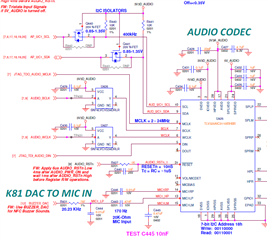

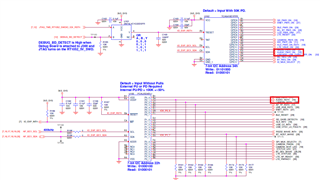

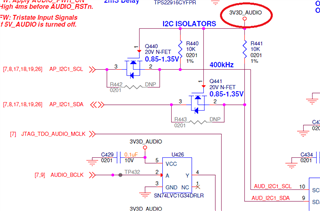

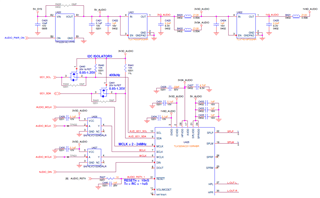

Good morning. Please help to review the following circuit.

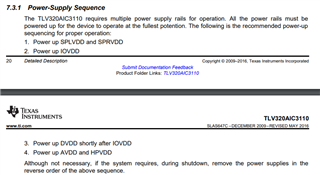

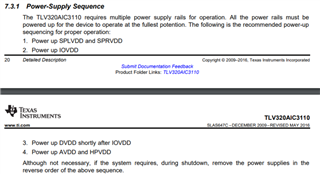

Does any concern about the power-on sequence and I2C communication sequence during power on stage?

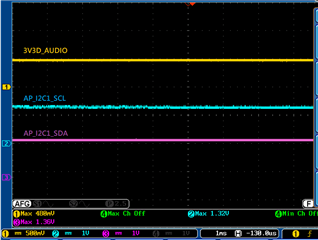

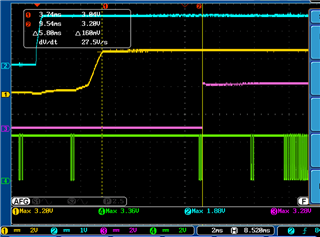

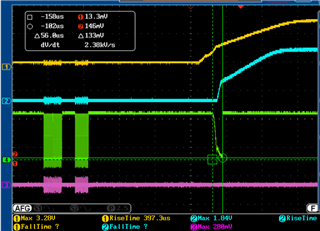

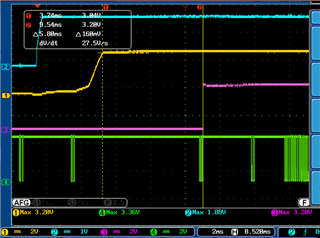

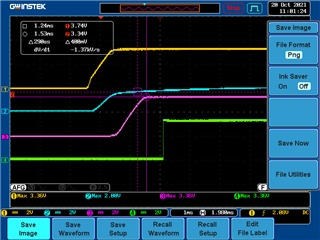

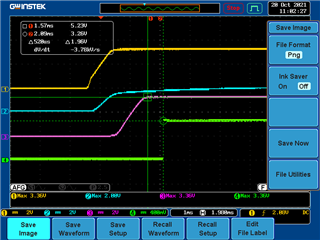

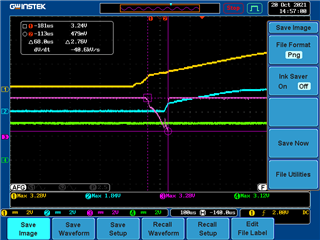

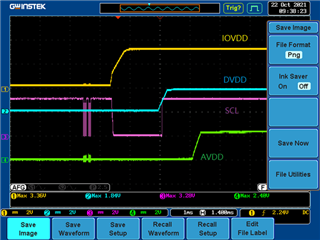

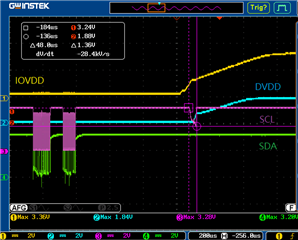

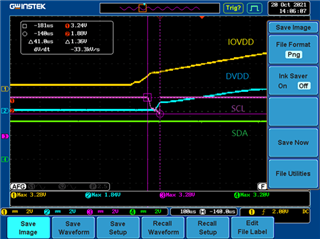

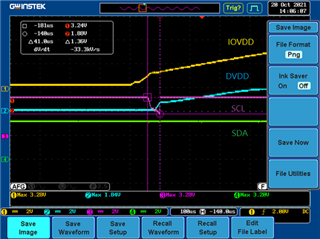

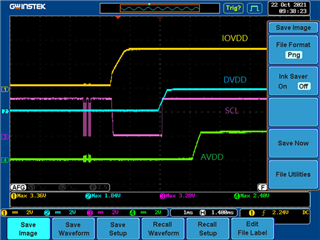

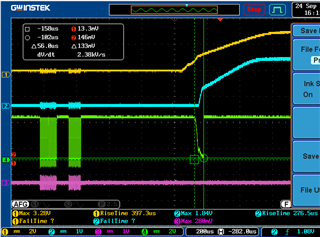

Some boards have abnormal symptoms(initialize stage) after Codec power on stage, which is I2C Clock assert a short time to low level at 1.8V power-on, then the I2C bus got stuck at a high level(3.3V),

and the Host's I2C bus doesn't work normal anymore.

Ch1 -> 3V3D_AUDIO

Ch2-> 1V8D_AUDIO

Ch4-> I2C1_SCL

Regards,

Joseph