In my application I'd like to use an the adc in slave I2S protocol to read 2 channels.

I'd like to know if is it possible to use FSYNC and BCK input to generate internal clock.

If yes could you share the PLL registers configuration?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

In my application I'd like to use an the adc in slave I2S protocol to read 2 channels.

I'd like to know if is it possible to use FSYNC and BCK input to generate internal clock.

If yes could you share the PLL registers configuration?

Hello,

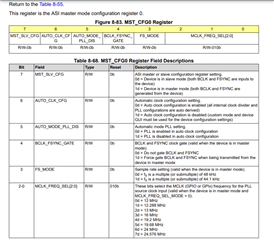

Keep this register in default state will allow you to supply a FSYNC and BCLK to generate internal clocks needed

Given the FSYNC to BCLK ratio being used is supported.

There is no other PLL registers necessary to configure if this register is left as it is and BCLK and FSYNC are supplied properly.

Best Regards,

Carson