Other Parts Discussed in Thread: , TAS2560, TAS2563

Hello,

I'd like to follow up on my previous post from a few months ago regarding using the TAS2559 in an embedded environment. Our hardware has arrived and I am trying to bring up the TAS2559 using the configuration sequence generated by PurePath Console 3 and the Python script you provided, but I am entirely unable to get the speaker to produce sound.

We are using an STM32 chip to program and enable the TAS2559 in a baremetal environment. I am currently using MCLK = 4.096MHz and BCLK = 1.28MHz hoping to support 16kHz 16-bit mono audio in Mono PCM Mode. To achieve this, I have set the audio frame length to 80 bits, as this triggers a pulse on the word clock at a rate of 16kHz. I can verify that these signals are being generated properly using a scope.

The configuration I am using immediately enables the speaker on the TAS2559EVM eval board with no additional configuration required. On our hardware, I have taken the following additional steps after programming the TAS2559 using the generated header file:

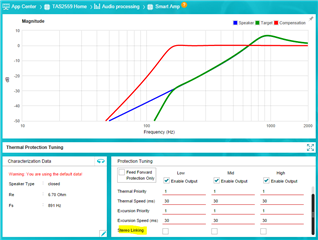

- Wrote 0x01 to register 0x22 DSP_MODE to manually set the chip to Smart Amp mode

- Set bits 1 and 2 in register 0x2A ASI_CTRL_1 to configure ASI1 to use monoPCM

- Wrote 0x01 to register 0x2F ASI_CTRL_2 to denote 16kHz sampling rate in PCM mode

- Set bit 7 in register 0x01 ASI1_FORMAT on page 1 to set the ASI1 input mode format to MonoPCM.

And I have also tried manually setting the following hardware configuration registers to match our hardware pinout, though all of the values programmed are listed as preferred: ASI1_BCLK, ASI1_WCLK, ASI1_DIN_DOUT, GPIO2_PIN, GPIO4_PIN, GPI_PIN.

Still nothing sounds.

All of the power lines on our board are as specified and within tolerance. I have checked all of the documented status registers. Everything is powered on and nothing reports any voltage, current, or clocking errors. We are programming the TAS2559 using an I2C bus and all of the writes are ACKed, and I can correctly read back written register values, so I believe that the chip is receiving its program correctly. I have even tried running the device in ROM mode 1 (PCM input playback only) just to get some sort of sound out of the device but nothing works. Is there anything I'm missing?

Some additional information: When I could not get the evaluation board to produce sound in my last post, the issue was a clocking mismatch. Here I am sure that I have correctly configured the chip to expect 4.196MHz from MCLK. Is it possible that either BCLK or WCLK are causing issues? None of the clock values selected are set in stone, though BCLK and the frame length are selected to configure a 16kHz WCLK. Perhaps it's also possible that the 80-bit frame length is causing data issues? The documentation specifies that the rising edge of the word clock denotes the (n-1)th data bit, but we are sending 16 data bits in the first 16 clock cycles of an 80-bit frame. I expect the remaining 64 bits in the frame to be ignored; is this the case?

I have attached the configuration file and its generated C header file as well.

Thanks,

Sam