Part Number: TLV320AIC23

Hi team,

I got a question from customer.

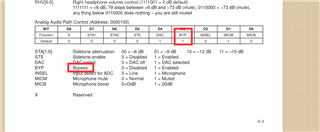

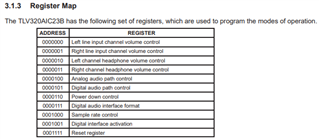

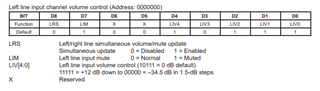

The audio solution is made up of 28335PGFA+TLV320AIC23IPW. There will be current noise with ordinary headphones, but the current noise that can adjust the volume of some headphones can be offset. What is the problem?

The following is the schematic diagram:

Please make some suggestions,Thank you very much for your help.

Best regards,