We have a design which uses the PCM6480-Q1 as a 4 channel DC coupled mic level ADC. We are talking to is over the SPI interface. The part is configured as the timing master for I2S audio. We do follow the procedure to wake the part (Page 0, r0x02 = 0x81), and wait for 2mSec before writing to the registers. After I update all of the registers to initialize the part ( including setting r0x75 to 0x60 to power up the ADC and PLL) I have NO activity on the SDout pin. We also occasionally get the Fsync output to drop out for a short period and restart.

I have connected the part in my product to the PCM6240 Eval board and downloaded the same register data and found the part to generate the I2S clocks and SDout data correctly.

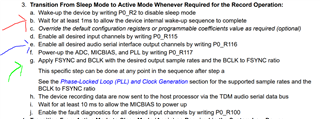

This leads me to believe that the timing of register updates and powering up the ADC and PLL is critical. The Eval board has a lot of delays (10's of mSec) between register writes. It even has a write to register 0x7f which I have not found documentation on.

1) How long after changing PLL registers do I have to wait before Enabling the input channels (register 0x73) or the ASI_OUT_CH_EN (r0x74)?

2) How long do I have to wait after enabling the input channels and ASI_OUT before Updating the PWR_CFG (r0x75) to power up the ADC and PLL?

3) Are there any diagnostics that shut down the ADC that I need to service?

I'm sure I am missing something simple here.

Thanks for your help

Mitch