We are trying to replace a digital receiver and an ADC in an existing product with the PCM9211. At first glance, it appears like it would be a very good fit. But after digging into the details, I'm not sure if it can do what we need it to do.

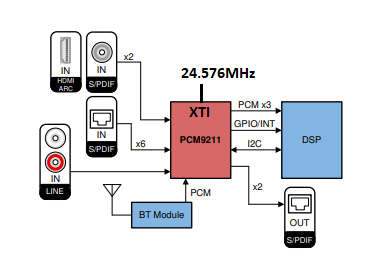

Our system configuration looks like this:

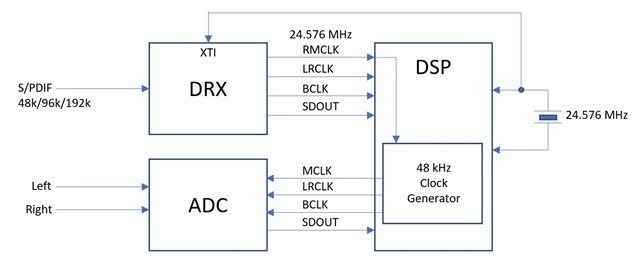

The digital receiver we're currently using always provides a valid RMCLK (Recovered MCLK -- either a recovered 24.576 MHz clock (when the DRX is locked) or the XTI input 24.576 MHz clock (when the DRX is not locked)). The DRX S/PDIF input can be either 48 kHz, 96 kHz or 192 kHz. The ADC is a slave, and always runs at 48 kHz. The ADC clocks are derived from the DRX RMCLK by a clock generator in the DSP, so the ADC is always in sync with the DRX (but possibly at either 1/2 or 1/4 the rate). If there is no S/PDIF input connected, the DRX is not locked and the 24.576 MHz XTI clock is used to generate the ADC clocks, and in this case the DRX data doesn't matter because there isn't any.

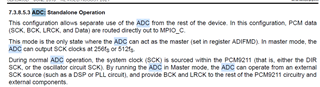

I can't seem to figure out how to do this with the PCM9211. I found the E2E post that explained that for the ADC to run in slave mode at a particular sample rate, the MCLK must be fed into the XTI input and the ADC configured to clock from XTI.

And from the PCM9211 datasheet section 7.3.1:

"When the PLL is locked, the secondary clock source automatically selects the PLL clock (256fS). Otherwise, the XTI clock source is selected. Register 32h should be used for dividing in the lock status (that is, the PLL source). When unlocked, Register 33h should be used (the XTI source)."

It seems like this is a "chicken or egg" problem. The SCKO is either the PLL clock or the XTI clock. But the XTI clock needs to come from the DSP clock generator (which uses SCKO as its input) to run the ADC in slave mode locked to the SCKO clock. That isn't going to work.

So I'm a little confused as to what to do here, or if there is evan a way to do what I'm describing with the PCM9211. Any insight would be very much appreciated.

Thank you!

-Dan