Hi,

At power up, during 5 ms the voltage of the I2C signal is higher than the IOVDD voltage.

Reset signal is down during power up.

Is there may affect device reliability?

Regards,

Regis

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

At power up, during 5 ms the voltage of the I2C signal is higher than the IOVDD voltage.

Reset signal is down during power up.

Is there may affect device reliability?

Regards,

Regis

Hi,

We may be considering changing timings and in this case we should have at power up during 240 ms the voltage of the signal MCLK= 2,8V, the voltage of the signal WCLK= 1V, the voltage of the signal DIN= 1,5V, the voltage of the signal Dout= 1V,the voltage of the signal BCLK= 1,1V and the voltage of the signal I2C=1,5V are higher than the IOVDD voltage . During this power up reset signal is down. See attach file. It is only during power up. Is it ok for device reliabilitysoft new bootloader-00020--00000.pdfsoft new bootloader-00025--00000.pdfsoft new bootloader-00026--00000.pdfsoft new bootloader-00027--00000.pdf

Hi,

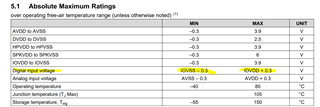

You should keep your digital level within this spec since your level is higher than IOVDD and all your supplies should be up during reset low see section 7.3.1 to 7.3.2.