Other Parts Discussed in Thread: TLV320AIC3101

Hi,

I don't know if I understand the register Settings correctly:

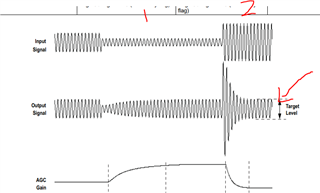

My camera wants to record in a noisy environment, and expects the output is stable at 78dB,but the ambient volume is about 90dB, so I want to use the AGC function.

skl_device -R "0x00,0x00;"//write in page 0

skl_device -R "0x0f,0x00;0x10,0x00;"//PGA gain =0dB

skl_device -R "0x13,0xc4;0x16,0xc4;"//input level control gain =-12dB

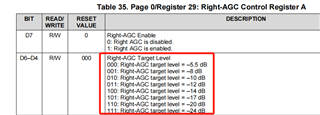

skl_device -R "0x1a,0x8c;0x1d,0x8c;"//AGC target level =-5.5dB,attack time =20ms,decay time=100ms

skl_device -R "0x1b,0x00;0x1e,0x00;"//AGC max gain =0dB

skl_device -R "0x20,0xe8;0x21,0xe8;"//Left-AGC gain =-12dB

skl_device -R "0x1c,0x7d;0x1f,0x7d;"//noise threshold =-88dB

skl_device -R "0x0c,0xa0;"//HPF Fc=600Hz

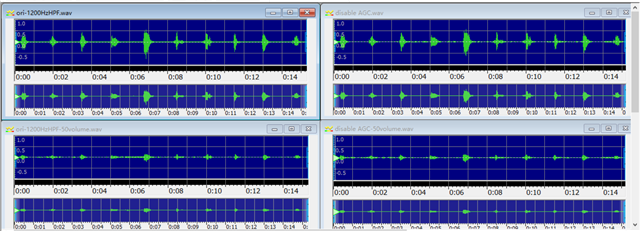

After I set this register, the recorded sound becomes very quiet,In about 35 db.

Meanwhile,if I record a 60dB source, my PGA gain and AGC max gain are set to 42dB, and input level control gain and Left-AGC gain from -12dB to 0dB,

the recorded sound was only about 68dB, only 8dB increse.

How do I set the target value for AGC? I don't quite understand the meaning of target level described in the specification.

Please help. many thanks.