Hi team,

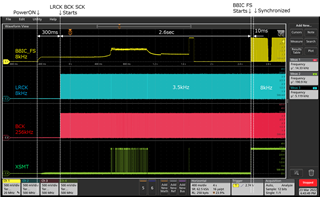

Customer use PCM5101A as slave. During normal operation, input clock is as following. and LRCK is synchronized with a clock named BBIC_FS.

LRCK: 8kHz (sync with BBIC_FS)

BCK: 256kHz

SCK: 2.048MHz

Before normal operation, there are not BBIC_FS but other clocks exist. During this time, LRCK is 3.5kHz. Based on this situation and attached waveform, please answer question?

Q1. Is there any problem with 3.5kHz LRCK before normal operation?

Q2. It looks like that LRCK sync with the half-way BBIC_FS. Is there any issue at this clock varies?

Best regards,

Hideki