Dear Team,

we are in the stage of evalution of audio amilifier ,there is option to give external mclk to the IC ,in that i have some doubts

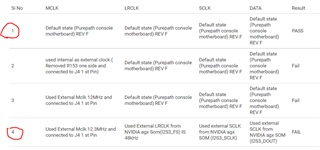

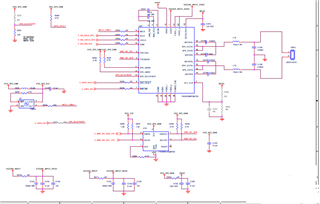

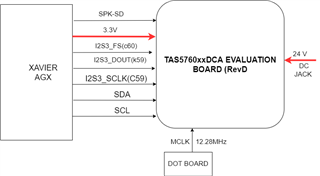

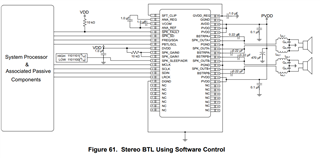

1) iam playing different kind of audio but i got only 48MHz how to changes sample frequency

2) if in case i want give external mclk what are the changes required in schematic.

Kindly help us on this stage

Thanks

pooja ak