- In our custom project, we are interfacing codec (TLV320AIC3120IRHBT) to Vocoder(AMBE-4020 Full-Duplex BGA) i.e, digital audio data is sent through I2S to vocoder.

- The requirements of I2S interface that are calculated wrt to vocoder are :

- I2S will be operated in DSP master mode

- The I2S interface allows the AMBE-4020

to receive and transmit 8 kHz speech data (Please refer 2.11 of AMBE-4020 Full-Duplex BGA) i.e, WS/FS/LRCLK/WCLK = 8 Khz

- Word length = 16

- No of channels = 2

- SCLK/BCLK = WCLK x Word length x No of channels = 8 Khz x 16 x 2 = 256 Khz

- Codec clock calculation for ADC:

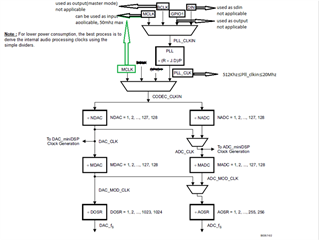

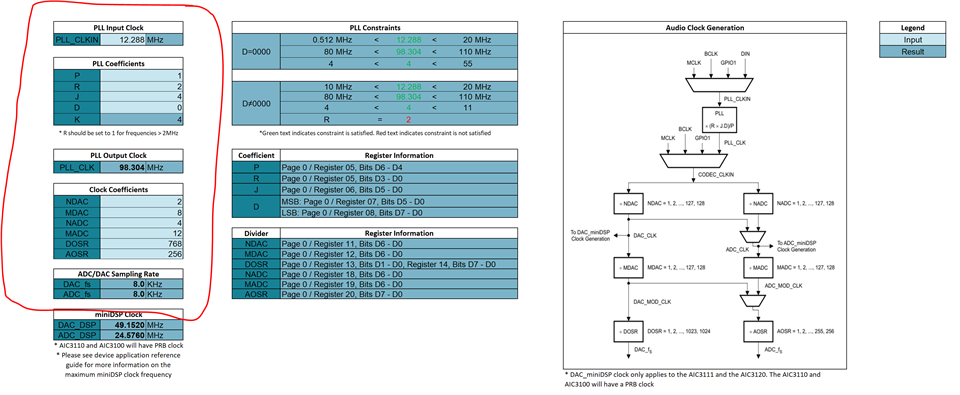

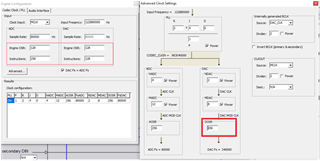

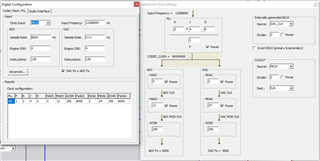

Following the procedure mentioned in section 7.3.10.8 step 1 and the clock calculation mentioned in the section 7.3.13. Inserted images for reference

- The targeted ADC sampling Frequency (ADC_Fs) = 8 Khz, obtained from 2.b which has been stated above.

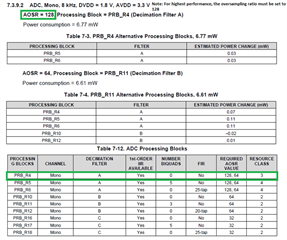

- Decimation filter = A

- AOSR = 128,

Selected b, c values by referring the section 7.3.9.2

- So, ADC_Fs x AOSR = 8 Khz x 128 = 1024 Khz = ADC_MOD_CLK. So given that 2800Khz ≤ AOSR*ADC_Fs ≤ 6200Khz (in section 3.10.8) but this condition is not satisfying, how to solve this?

- The value of MADC should be chosen such that it satisfies the condition MADC*(AOSR/32)>=RC. So chosen MADC = 1. Is the calculation for MADC correct? Since in documentation it is said that it can be in the range of 1 to 128 and no further information is provided on this.

- So if the MADC which is chosen is correct, then ADC_CLK = ADC_MOD_CLK x MADC = 1024 Khz x 1 =1024 Khz. Please suggest on what basis the frequency of ADC_CLK will depend and its range?

- What shall be the value of NADC to be chosen to get the CODEC_CLK (CODEC_CLK = NADC x ADC_CLK). Please suggest on what basis the frequency of CODEC_CLK will depend and its range?

- Also please suggest the values for PLL and frequency of MCLK, if incase PLL input is used as a CODEC_CLK and provided MCLK as an input to PLL.