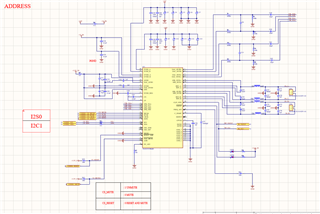

We have a design that uses TAS3251 to run a 2-speaker BTL with a capacity of 50W/1 channel

I use 3 pin I2s communication for TAS3251.

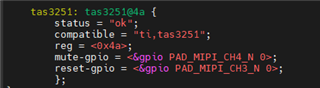

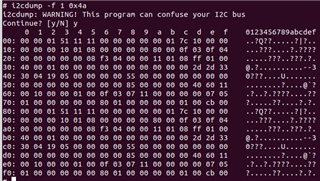

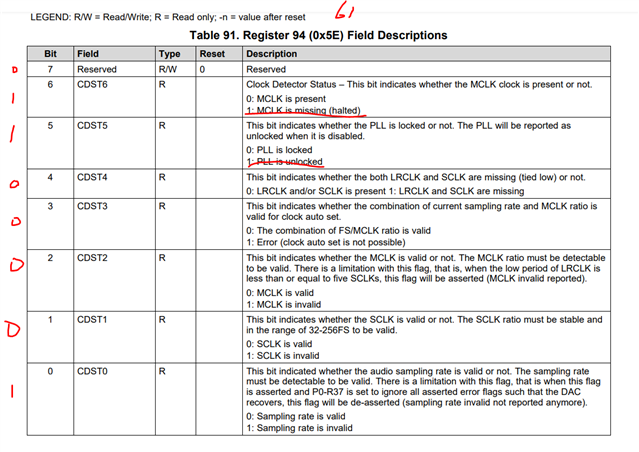

while the audio output works fine however some cases of sudden loss of sound I have tried restarting the MCU to re-init the TAS3251 registers however it doesn't work, only when I restart the source for TAS 3251, the device will work again.

When touching the heatsink of the TAS3251, I noticed that the sound fluctuates, maybe the I2s line is getting noisy. However, the error occurs even with devices that are not interfered with.

Looking forward to your help

this is my TAS3251 schematic (MCLK pin is not connect):