Other Parts Discussed in Thread: TLV320AIC3262

Hi Team

Noticed AIC3268 has 3 lanes I2S interface. do they can work simultaneously with different clock sample rate?

if not, is there any other device can meet this requirement?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team

Noticed AIC3268 has 3 lanes I2S interface. do they can work simultaneously with different clock sample rate?

if not, is there any other device can meet this requirement?

"This enables three simultaneous digital playback and record paths to three independent digital audio buses or chips. Each of the Digital Audio Serial Interfaces can be run using separate power voltages to enable easy integration with separate chips with different IO voltages." Also section 8.3.9.2.3 of d/s specifies how to setup multi-channel i2s configurations.

Also in Figure 85 of d/s there are 2 frame clock (WCLK) inputs to DIN thus supporting different sample rates.

Regards

Hi Daveon

Thanks for your respond.

I noticed the clock source of DAC or ADC can derive many source. these ADCs or DAC can be configure as different frequency rate simultaneously or only one rate simultaneously? if all DACs can only works at one rate at one moments?

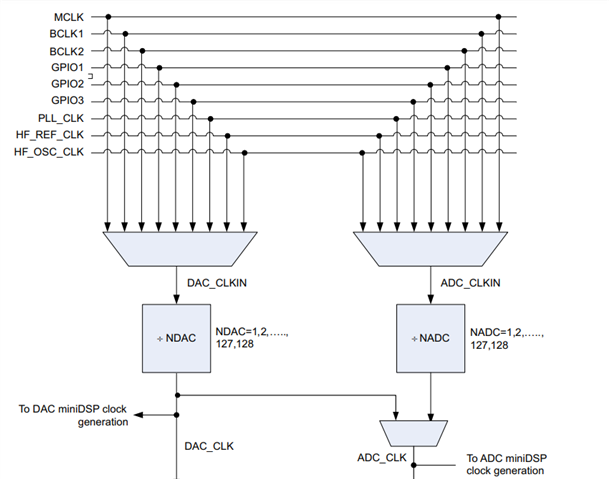

The DAC/ADC Fs derived from the PLL can be both different rates simultaneously or one rate simultaneously depending on the values of NADC/NDAC, AOSR/DOSR, or MDAC/MDAC in combination with the frequency of the input source. Each block is an independent value shown in table 25.

Hi Daveon

Thanks for your respond! Understand that DAC and ADC can works as different frequency simultaneous. how about left ADC and right ADC, Can they work as different frequency simultaneous? and how about left DAC and right DAC?

Hi Harry,

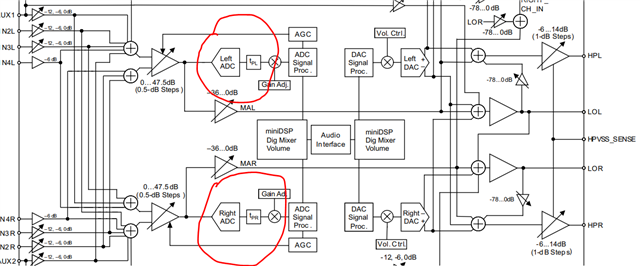

In the existing portfolio of CODEC, we have TLV320AIC3262 that supports asynchronous different sample rates for ADC & DAC.

For playing back audio/speech signals at various sampling rates, AIC3262 provides an efficient asynchronous sampling rate conversion with the combination of a dedicated ASRC coefficient calculator and the DAC miniDSP engine. The coefficient calculator estimates the audio/speech data input rate versus the DAC playback rate and feeds the calculated coefficients to the miniDSP, with which it converts the audio/speech data to the DAC playback rate. The whole process can be configured automatically without the need of any input sampling rate related information. The input sampling rates as well as the DAC playback rate are not limited to the typical audio/speech sampling rates. A reliable and efficient handshaking is involved between the miniDSP software and the coefficient calculator. For detailed information, please refer to the AIC3262 software programming manual - https://www.ti.com/lit/ug/slau309/slau309.pdf?ts=1669296165145

Also, kindly request you to not create parallel email and e2e threads. Let's continue our on-going conversation on the email. Thanks for understanding!

Best Regards,

Sakshi