Hi!

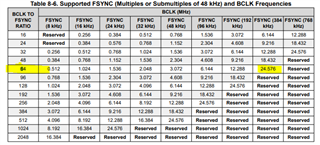

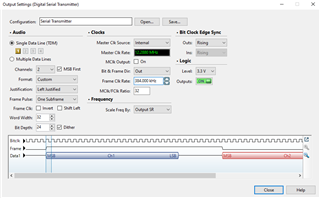

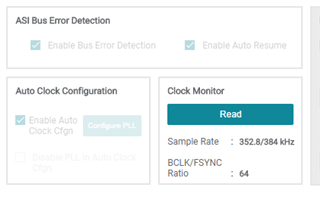

I believe digital mixer is preventing me from sampilng at 384KHz- please let me know if I am fixating on the wrong thing! I am hoping to get a 384KHz sample rate with DECI_FILT = 10 (ultra low latency). I’ve been able to get this setup working on 2 channels at 32 bit word length and at 192 kHz but I haven’t been able to get up to 384 kHz

In section 3.5 of app note, AGC, DRE, DRC, bi-quads, channel summers, and digital mixer processing blocks are not supported for 384 kHz operation https://www.ti.com/lit/an/sbaa494a/sbaa494a.pdf

From my understanding, CH_SUM[1:0] must be 00. However, table 2-5 mentions [00] = Channel summing mode is disabled (Digital Mixer is enabled).

Would this prevent me from getting desired 384KHz? Anything else to look at?

Thank you,

Cameron Wutzke