Dear Sir or Madam,

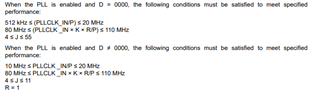

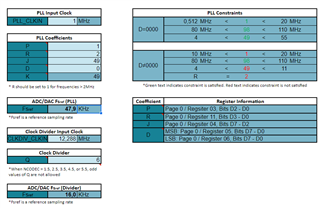

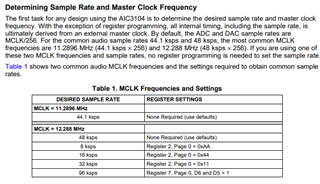

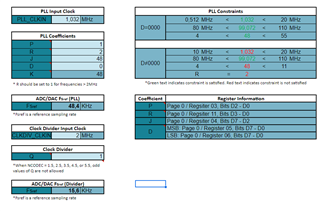

I'm currently using the TLV320AIC3104 and I'd like to use the PLL in order to generate the Audio Clock. I provide a 512kHz MCLK and I'd like to have a sampling frequency of 16kHz (data width of 16 bits). I don't understand how I am supposed to compute the different coefficients. I tried the xlsx file but still I can't find any matching combination.

Could you explain me how all this work ?

Have a nice day,

Kind regards,

William.