Hi TI Team,

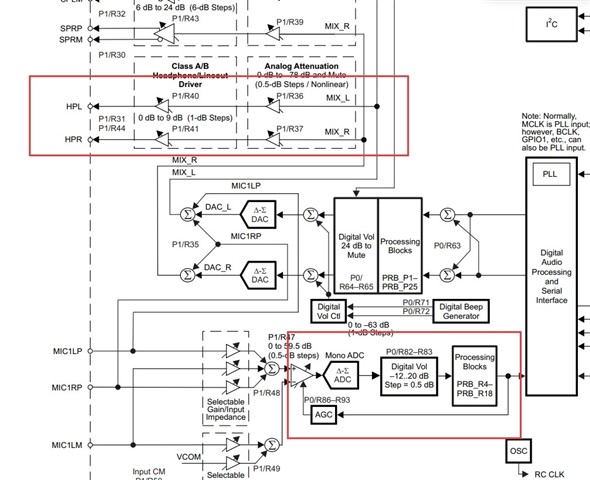

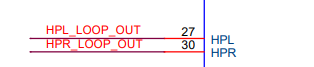

At present, we can use TLV320AIC3110 chip to independently switch on the recording module (ADC), loop out module (HPL & HPR),

However, when loopout and recording are enabled at the same time, that is, when the functions of the two modules marked in the figure are enabled, loopout function will produce recording effect

Impact, recording files have relatively large noise.

Attached "TLV320AIC3110 Recording Noise problem.docx" is debugging related data, as well as recording files in two cases.

Please help to deal with this problem.