Hello,

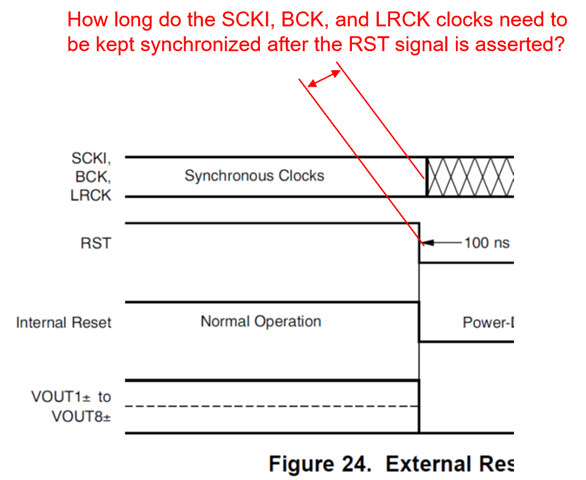

PCM1690's data sheet describes in the section 7.3.5 Reset Operation, "Figure 24 shows a timing diagram...If RST goes from high to low under synchronization among SCKI, BCK, and LRCK, the internal reset is asserted, ..." What if RST goes from high to low when these audio clocks are NOT synchronized? In this case, won't the internal reset be asserted? I'd like to confirm whether the internal reset is asserted or not when any of the audio clocks are not provided.

Best regards,

Shinichi Yokota