Other Parts Discussed in Thread: ADS127L01

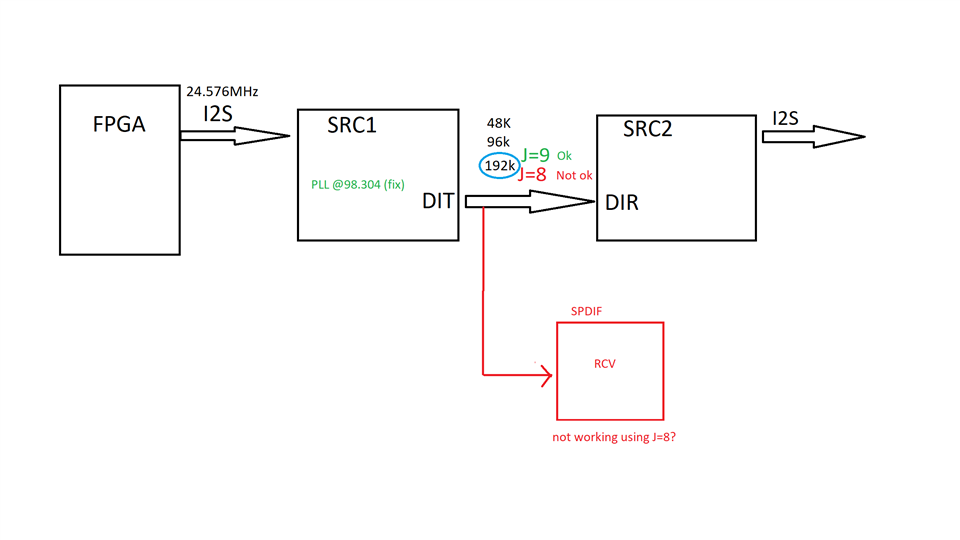

I have 2 SRC4392 running off the same 24.576MHz MCLK.

- Port A (192kHz I2S slave) => SRC => DIT (48kHz, 96kHz, or 192kHz)

- DIR => SRC => Port A (192kHz I2S slave)

I have PLL1 configured as recommended in the DS (P=2, J=8, D=0) to get 98.304MHz. Everything works great at 48kHz and 96kHz, but at 192kHz, the lock is sporadic and the received channel status jumps all over; sometimes correct and sometimes random.

If I change the PLL1 to 110.592MHz (P=2, J=9, D=0), 192kHz audio appears to work.

The DS states

Registers 0x0F through 0x11 are utilized to program PLL1 in the DIR core. PLL1 multiplies the DIR reference clock source to an oversampling rate which is adequate for AES3 decoder operation

and then provides calculations to get as close as possible to 98.304MHz.

Is this a magic frequency with consequences if PLL1 is set to another frequency?

Thanks,

Jon