I have used AIC3100 with nxp imx8mm,i have integrated codec driver of AIC3100 with linux kernel. Now codec register successfully, but when i try to play wav file using tinyalsa it gives error as "Error Playing File".

Device tree configuration:

sound-tlv320aic31xx {

+ compatible = "simple-audio-card";

+ simple-audio-card,name = "tlv320aic31xx-codec";

+ simple-audio-card,format = "i2s";

+ simple-audio-card,frame-master = <&cpudai2>;

+ simple-audio-card,bitclock-master = <&cpudai2>;

+ /*simple-audio-card,mclk-fs=<256>;*/

+ simple-audio-card,widgets =

+ "Headphone", "Headphone Jack";

+ simple-audio-card,routing =

+ "Headphone Jack", "HPL",

+ "Headphone Jack", "HPR";

+

+ cpudai2:simple-audio-card,cpu {

+ sound-dai = <&sai2>;

+ };

+

+ simple-audio-card,codec {

+ sound-dai = <&tlv320aic31xx>;

+ clocks = <&codec_osc>;

+ };

+ };

+

+ clocks {

+ codec_osc: aud_mclk {

+ compatible = "fixed-clock";

+ #clock-cells = <0>;

+ clock-frequency = <24000000>;

+ clock-output-names = "codec-mclk";

+ };

+ };

SAI2 clock:

@@ -118,8 +194,9 @@ &sai2 {

pinctrl-0 = <&pinctrl_sai2>;

assigned-clocks = <&clk IMX8MM_CLK_SAI2>;

assigned-clock-parents = <&clk IMX8MM_AUDIO_PLL1_OUT>;

assigned-clock-rates = <24576000>;

- status = "disabled";

+ status = "okay";

};

Codec was able to detect in I2C node:

tlv320aic31xx:codec@18 {

+ compatible = "ti,tlv320aic3100";

+ reg = <0x18>;

+ #sound-dai-cells = <0>;

+ /* Regulators */

+ AVDD-supply = <®_3p3v>;

+ HPVDD-supply = <®_3p3v>;

+ SPRVDD-supply = <®_5v>;

+ SPLVDD-supply = <®_5v>;

+ DVDD-supply = <®_1p8v>;

+ IOVDD-supply = <®_1p8v>;

+

+ ai31xx-micbias-vg = <1>;

+ };

Issue:

root@picoimx8mm:/home/ubuntu# dmesg | grep tlv

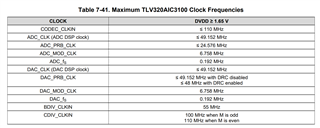

[ 40.059531] tlv320aic31xx-codec 1-0018: aic31xx_set_dai_sysclk: Unsupported frequency 24576000

[ 40.088026] tlv320aic31xx-codec 1-0018: ASoC: error at snd_soc_dai_set_sysclk on tlv320aic31xx-hifi: -22

[ 40.121946] tlv320aic31xx-codec 1-0018: simple-card: set_sysclk error

[ 40.138078] 30020000.sai-tlv320aic31xx-hifi: ASoC: error at snd_soc_link_init on 30020000.sai-tlv320aic31xx-hifi: -22

[ 40.168804] asoc-simple-card: probe of sound-tlv320aic31xx failed with error -22

root@picoimx8mm:/home/ubuntu#

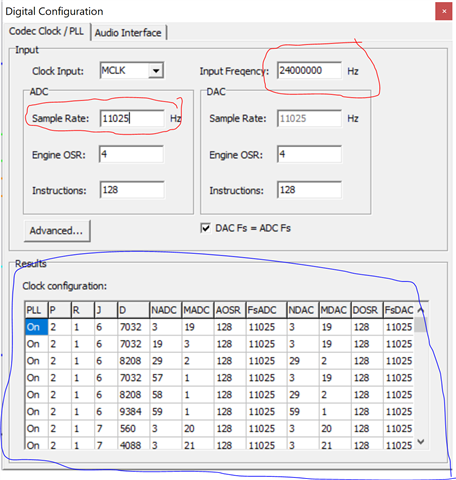

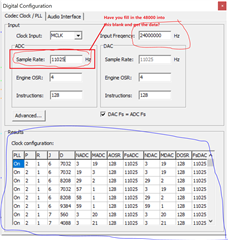

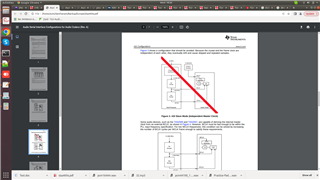

Externally feeding the 24MHZ oscillator to the codec MCLK, but the codec driver was not supporting.

sound/soc/codecs/tlv320aic31xx.c (No 24Mz support)

/* ADC dividers can be disabled by configuring them to 0 */

static const struct aic31xx_rate_divs aic31xx_divs[] = {

/* mclk/p rate pll: j d dosr ndac mdac aors nadc madc */

/* 8k rate */

{12000000, 8000, 8, 1920, 128, 48, 2, 128, 48, 2},

{12000000, 8000, 8, 1920, 128, 32, 3, 128, 32, 3},

{12500000, 8000, 7, 8643, 128, 48, 2, 128, 48, 2},

/* 11.025k rate */

{12000000, 11025, 7, 5264, 128, 32, 2, 128, 32, 2},

{12000000, 11025, 8, 4672, 128, 24, 3, 128, 24, 3},

{12500000, 11025, 7, 2253, 128, 32, 2, 128, 32, 2},

/* 16k rate */

{12000000, 16000, 8, 1920, 128, 24, 2, 128, 24, 2},

{12000000, 16000, 8, 1920, 128, 16, 3, 128, 16, 3},

{12500000, 16000, 7, 8643, 128, 24, 2, 128, 24, 2},

/* 22.05k rate */

{12000000, 22050, 7, 5264, 128, 16, 2, 128, 16, 2},

{12000000, 22050, 8, 4672, 128, 12, 3, 128, 12, 3},

{12500000, 22050, 7, 2253, 128, 16, 2, 128, 16, 2},

/* 32k rate */

{12000000, 32000, 8, 1920, 128, 12, 2, 128, 12, 2},

{12000000, 32000, 8, 1920, 128, 8, 3, 128, 8, 3},

{12500000, 32000, 7, 8643, 128, 12, 2, 128, 12, 2},

/* 44.1k rate */

{12000000, 44100, 7, 5264, 128, 8, 2, 128, 8, 2},

{12000000, 44100, 8, 4672, 128, 6, 3, 128, 6, 3},

{12500000, 44100, 7, 2253, 128, 8, 2, 128, 8, 2},

/* 48k rate */

{12000000, 48000, 8, 1920, 128, 8, 2, 128, 8, 2},

{12000000, 48000, 7, 6800, 96, 5, 4, 96, 5, 4},

{12500000, 48000, 7, 8643, 128, 8, 2, 128, 8, 2},

/* 88.2k rate */

{12000000, 88200, 7, 5264, 64, 8, 2, 64,

TI driver tlv320aic3100 codec driver doesn't have 24MHZ support Please support us to resolve the issue?

Regards,

SanthanaKumarS