Hello,

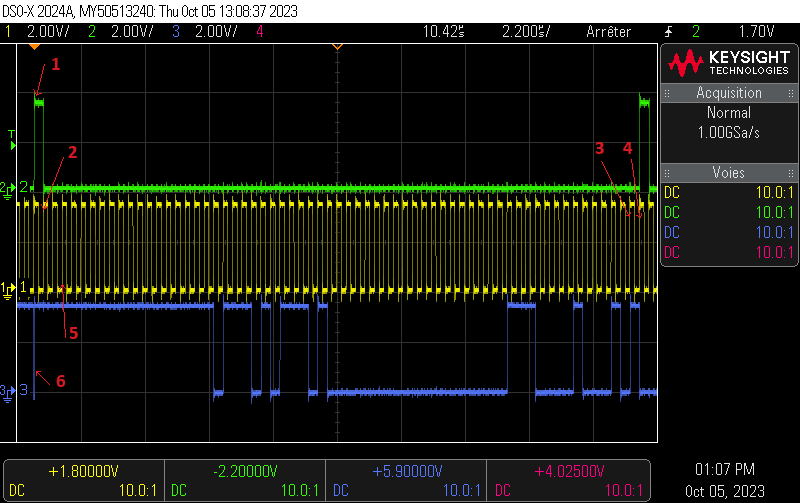

I'm using TLC320ADC6140 in slave mode connected to a STM32 processor. TDM mode, 2 slots of 32 bits, no TX offset, default polarity for FS, BCLK. FSYNC rate 48kHz and BCLK 3.08MHz.

Firsts test work fine, I get the result expected.

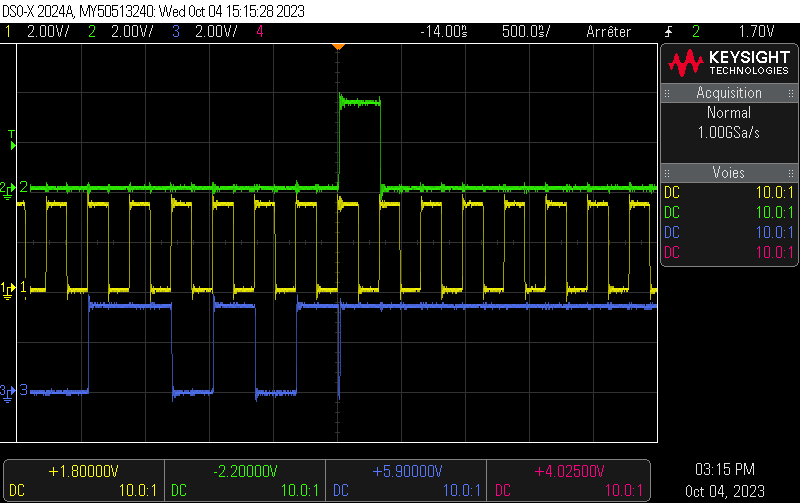

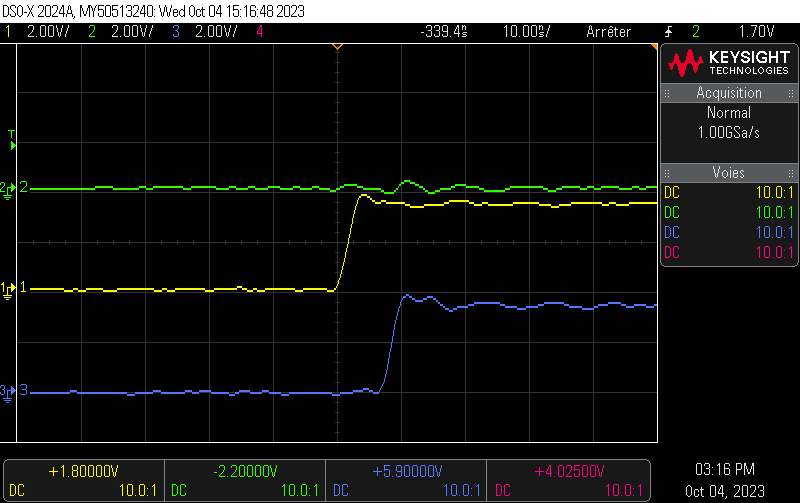

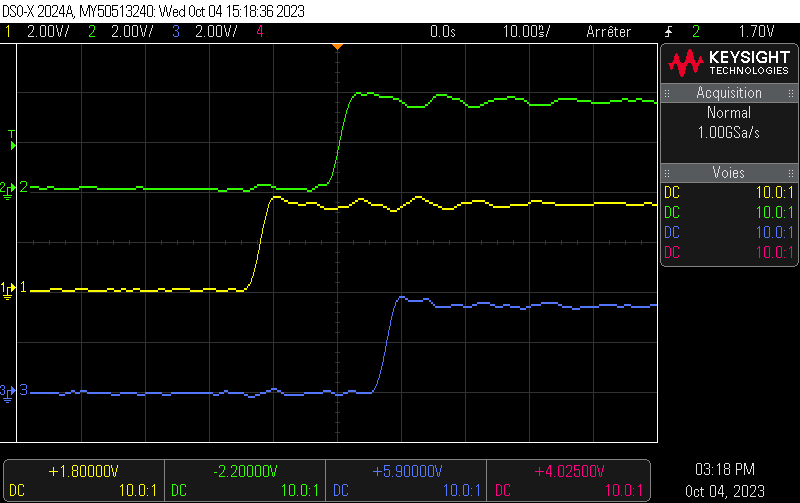

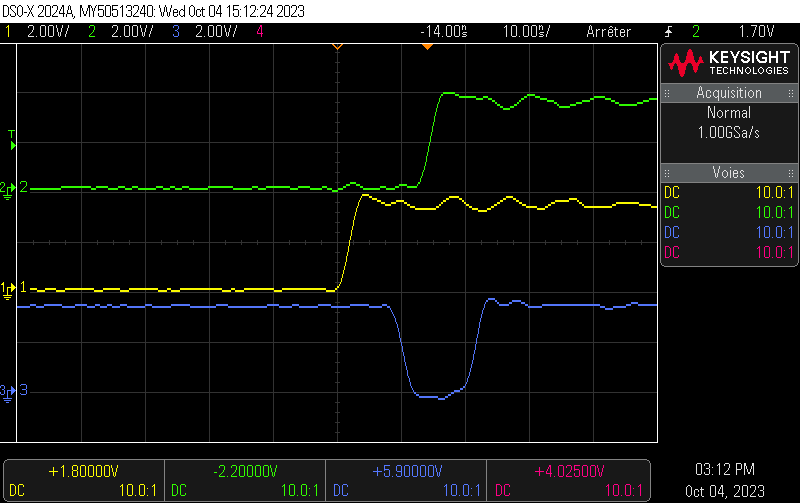

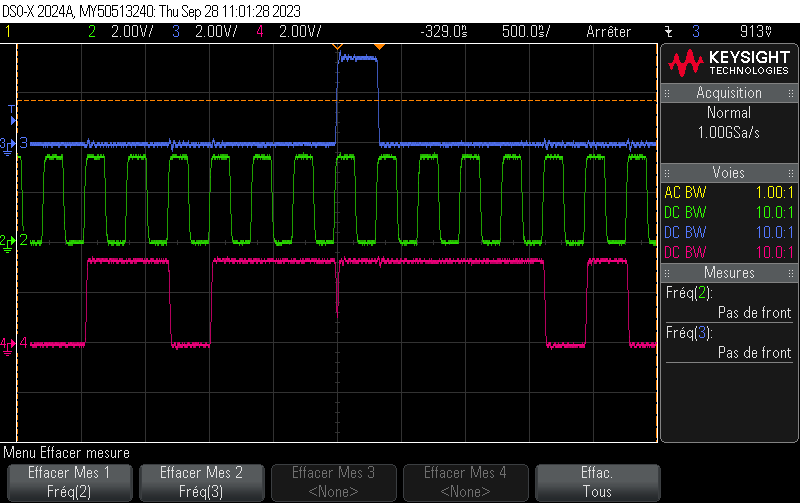

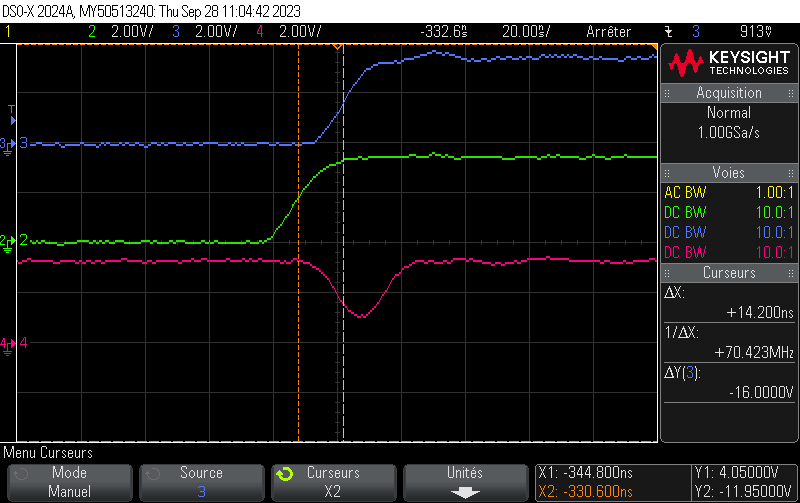

On the scope screen, we see that FSYNC rise about 15ns after BLCK edge. We can see on the screen that the TLV starts updating its output to a 0 (void fill) on the BCLK edge, but 15ns later, while the DOUT signal is still falling to 0, the FSYNC edge comes and the output is immediately updated with the MSb value of slot 0.

Blue = FSYNC, Green = BCLK, Red = SDOUT.

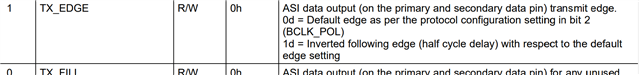

We can read in section 8.3.1.2.1 :

"In TDM mode, also known as DSP mode, the rising edge of FSYNC starts the data transfer with the slot 0 data first. {...} FSYNC and each data bit (except the MSB of slot 0 when TX_OFFSET equals 0) is transmitted on the rising edge of BCLK"

It says that the SDOUT signal is updated on the rising edge of BCLK, except for the MSB of slot 0, but without more explanation. It seems that the rising edge of FSYNC overrules the BLCK edge and forces SDOUT update, am I right ?

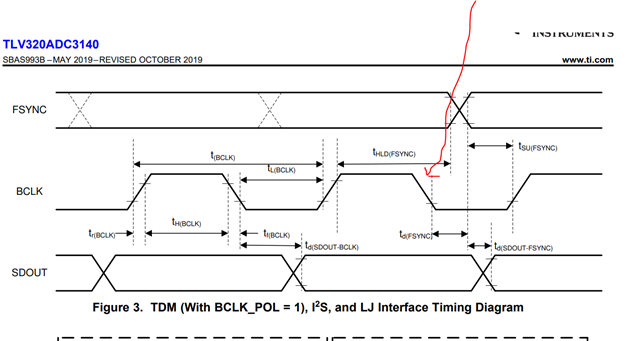

But I'm not sure of the margin I have on the FSYNC / BCLK edges timing. The TLC datasheet does not provide a lot of chronograms, and the only one for TDM mode is given for BCLK_POL = 1, and I'm not sure how it is linked to FSYNC edge in my config with BCLK_POL = 0.

What happens if the FSYNC edge comes too early after BLCK edge or is seen before BLCK edge (devices or layout tolerances) ? Is there a risk of loosing the MSB of slot 0 (that would be transfered on FSYNC edge, but replaced by the next data bit on the very next BLCK edge ?

Should I be in a more safe condition if I add a small RC on FSYNC to ensure minimum delay between BCLK rise and FSYNC rise (I already have 100R+22pF on each line) ?

Thank you

Aurelien