Tool/software:

Hi,

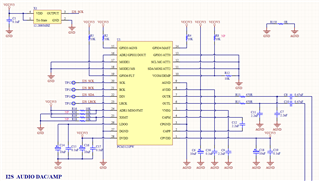

I am currently need a DAC that can provide I2S master in Hardware mode.

I know that the PCM5121 does not support I2S master in hardware mode.

However, when my colleague configure the PCM5121 to hardware mode, he is able to decode the signals and hear the desired audio. at 48KHz.

We would like to know why this is possible.

Can you also recommend any I2S DAC that can provide I2S master in hardware mode. We only require it to run at one sampling frequency

Thanks and Regards

Michael

,

,