Other Parts Discussed in Thread: TLV320AIC33

Tool/software:

We use multiple CODECs (TLV320AIC3204) connected to a host. To have control over the MCLK quality we have an external MCLK source and make one CODEC Master, the other CODECs and host are slave.

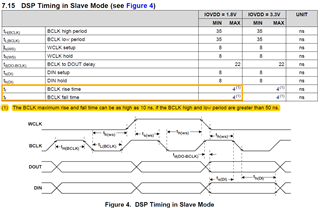

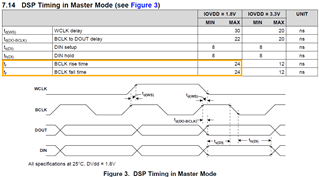

Checking the timing we discovered that the BCLK Output rise/fall time of the Master CODEC (< 24ns) doesn’t match with the BCLK Input rise/fall time requirement of the Slave CODEC (< 4ns and for a BCLK of 10MHz/100ns this may be relaxed to 10ns).

What is the rational behind this and why is there a mismatch?

May we relax the input rise/fall time more, given that our BCLK period time is 488ns?

Side note, the application note SLAA301 describes the "TDM Function to Interface Four TLV320AIC33 Codecs With a Single Host Processor". The TLV320AIC33 has the same issues w.r.t rise/fall time for the DSP Master and DSp Slave mode.

Thanks.