Other Parts Discussed in Thread: OPA1678, PGA4311

Tool/software:

Hello,

I'm using the PGA2311 in a product for approx. one year and it worked like a charm. No noticeable noise when changing volume. After the first two batches I changed from the PDIP package to the SOIC package and that's when the problems started. All of a sudden there is very noticeable noise when changing volume, especially above 0dB. These has two sources:

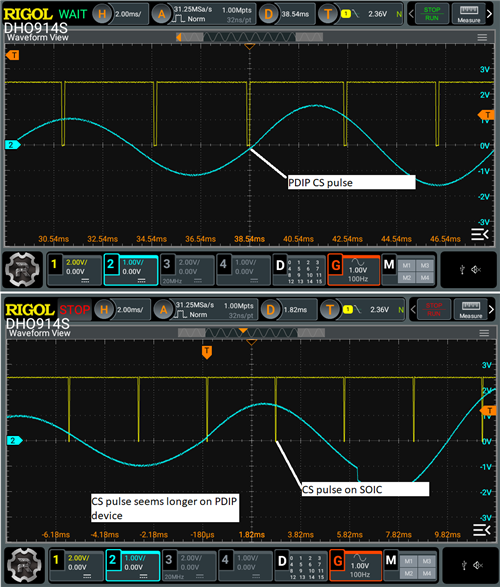

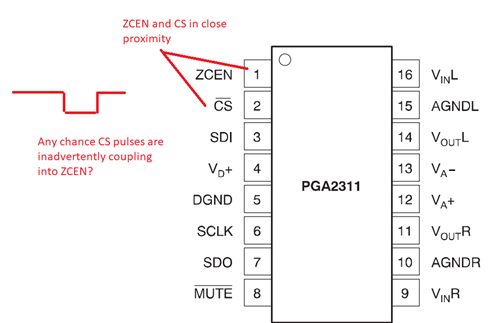

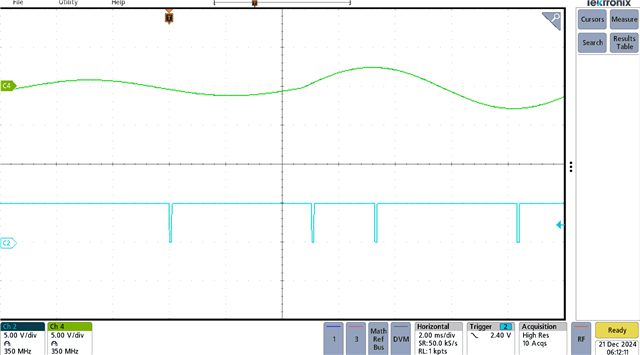

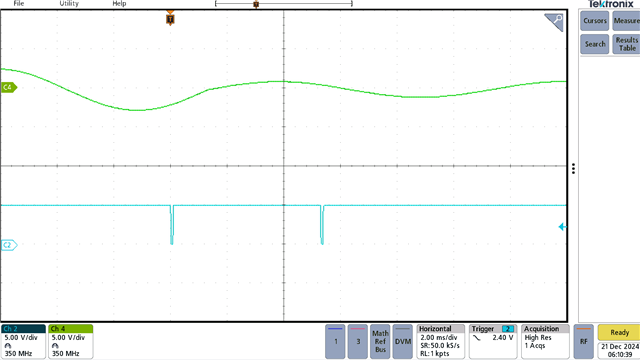

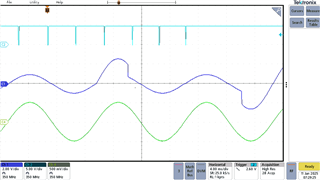

- The zero crossing detection started to behave oddly. It seems like the ZCD stops to work, when there are messages sent before the ZCD detects the zero crossing of a previous command. I only could get that under control with a waiting period of 18ms before sending the next message. This is a problem, because I need a very smooth fade and these 18ms waiting periods are noticeable under some circumstances.

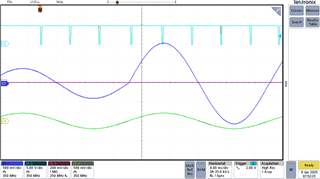

With the PDIP package the ZCD works like there is only a change in volume after a zero crossing or a timeout of 16ms. With the SOIC package there is an immediate change in volume, if the PGA2311 waits for the zero crossing of a previous volume change command and a new volume change command is issued. - The parts with SOIC package had a DC offset. I have a DC blocking capacitor on the input and with that the measured DC offset was up to +-500uV which results in a DC offset of some mV after the gain. This DC offset leads to a very strong swichting noise. To get that under control I had to remove the DC blocking capacitor and hand select opamps of the input stage to get a DC offset of under 100uV which resulted in the volume changes being quiet to up to +20dB. This wasn't the case with the PDIP package. I measured an old one with the PDIP package and it has almost 0uV DC offset.

Is there any information of changes between packages or even batches?