Tool/software:

We now encounter a customer service landline, the downlink speaker listens to a relatively low nasal tone (sample rate 8k), the ordinary phone does not have this situation (sample rate is 16k), the platform will go through the codec before the audio data exported to sound crisp.

We now encounter a customer service landline, the downlink speaker listens to a relatively low nasal tone (sample rate 8k), the ordinary phone does not have this situation (sample rate is 16k), the platform will go through the codec before the audio data exported to sound crisp.

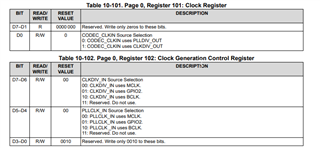

Refer to other projects also used codec 3104, using I2S, using mclk, there is no such problem as above.

Now the difference between the two projects is that the project with nasal sound does not connect to mclk, and uses bclk. For reference, another project also uses bclk but uses DSP mode, and the sound is also crisp.

So I would like to consult:

1. What configuration needs to be changed with bclk codec driver or what exclusions are there?

2. Use bclk or do you have to use DSP mode to have no problems?

Please help to see what is the current problem and how to solve it?