Tool/software:

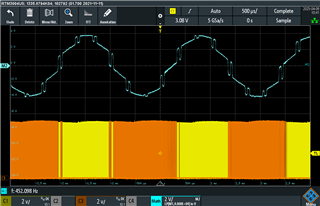

I have a TAS2563YBG EVM, and it's connected to custom bare-metal hardware for I2S and I2C. If I run my I2S bus with a 48kHz sample rate, everything works just fine, and I get a sine wave out without any noticeable distortion. If I run it at 96kHz, I get the attached "sine" wave. I have verified that the HW I2S bus has the correct data on it via a logic analyzer and exporting the captured data to WAV.

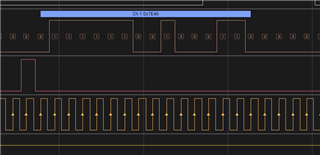

My audio bus is configured for 16-bit samples left justified in 32-bit slots, stereo, but with a TDM/DSP_A frame format (64 clocks per FS), where I have a single bit wide high level pulse, one bit before the first channel data. Data is valid on rising edge. See attached logic trace screenshot.

I have confirmed that as measured on the pins of the EVK, my signal integrity looks excellent. I have also tried configuring my audio bus for 48kHz, but 128 clocks per FS (so the same clock rate as 96kHzx64) to rule out clock frequency related issues and it performs identical to the 48kHzx64 configuration.

I am running 96kHz sample rate as I am planning on taking advantage of the "Full Scale Ultrasonic Output to 40kHz" as mentioned in the datasheet. I will both have intended content in the audio band, as well as ultrasonic.

I have just received access to the TAS2563 software (dated March 2020) for PPC3, but I note on the "Known Issues" sheet that "Ultrasound (96 KHz) is not supported for this release".

What do I need to do differently to initialize the TAS2563 to support 96kHz mode as claimed in the datasheet? My version of the datasheet (public as of time of writing) is "SLASET3D – APRIL 2019 – REVISED JANUARY 2024".

wr_spk_amp(0, 0); // Reset to page 0

wr_spk_amp(0x7F, 0x00); // Book 0

wr_spk_amp(1, 1); // Reset

vTaskDelay(100);

wr_spk_amp(0x02, 0x01); // Set Mute Mode

wr_spk_amp(0x03, 0x02); // AMP LEvel = 4VPK

wr_spk_amp(0x06, 0x08); // TDM Sync off, DSP-A

wr_spk_amp(0x07, 0x02); // DSP-A, 1 bit offset, sample rising

wr_spk_amp(0x08, 0x52); // mono left pcm + 16/32bits

wr_spk_amp(0x09, 0x10); // TDM RX Slots 0/1

wr_spk_amp(0x0A, 0x03); // TDM TX fill 0

wr_spk_amp(0x0B, 0x44); // TDM TX VSNS S4

wr_spk_amp(0x0C, 0x40); // TDM TX ISNS S0

wr_spk_amp(2, 0x00); // Set Active Mode