Tool/software:

We use TPA3138D2 for our AMP design , we find some protect issue need TI proivde detail information

Our Design Setting:

a)1SPW Mode

b)Stereo BTL output

c)PVDD 8V supply

d)20dB Gain

e)PLIMIT Set to GVDD

f)4 Ohm DCR speaker loading (impedance on some frequency impedance low to 3.2 Ohm)

Question:

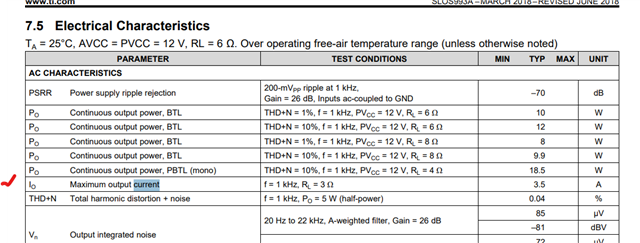

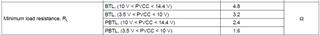

1.On the SPEC , BTL Model support 3.2 Ohm resistance , we want to know It is accept to driver 4 Ohm DC resistor (3.2 Ohm impedance at some frequency) speaker driver with +/- 20% and do not go into protect mode?

2.On the SPEC haven't OCP informaiton, We want to know 1SPW/BTL mode the over current information(Min/Max) @ IC 25C and 100C stage.

3.We are design the system sensitivity , and want to take more hearroom margin , When we use 30% clip's , below 5KHz sine wave(with 3R resistor load) amplifier work normal, when the frequency more than 5KHz, IC very easy to go into protect mode . Are the IC support high clip working mode ? if not , how many %'s clip is the up limit are your suggest (10%? 15%? 20%?) and confirm IC can work normal at 20Hz to 20KHz ?

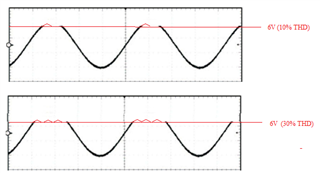

Normal design : DAC 0dBFS output , we are sestting Amplifier output around 10% Clip THD (0.5dB margin)

More hear-room design:DAC -10dBFS output , Amplifier output around 10% clip THD

DAC 0dBFS output , Amplifier output around 30% Clip THD