I have encountered a problem when interfacing PCM3794A codec to an FPGA. The codec is working in I2S SLAVE mode and all the timing is controlled by the FPGA. I need to have 8 kHz sampling rate and my system clock is 12.288 MHz.

With the following configuration:

fLRCLK = 8 kHz

fBCLK = 32 fLRCLK

fSCKI = 1536 fLRCLK = 12.288 MHz

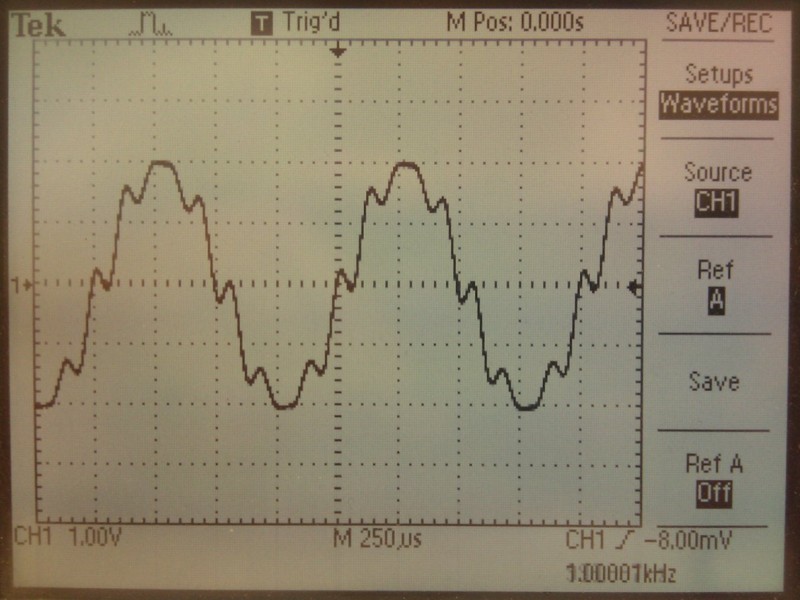

I get very distorted sine signal at the output:

System clock rate selection is set as recommended in the datasheet: MSR[2:0] = 111 and NPR[5:0] = 000000.

Changing MSR value has no effect on the output waveform. Changing NPR value results in shape change of the sine but none is perfect. I have also modified my FPGA interface to clock data bits at 64 fLRCLK rate but there is no difference.

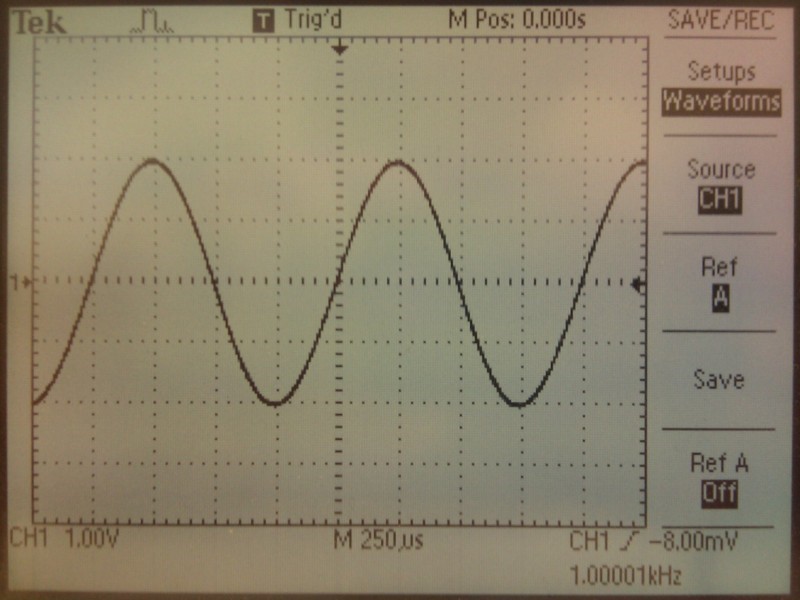

After decreasing SCKI frequency to 6.144 MHz (12.288 MHz / 2) the signal at the output looks as expected:

fLRCLK = 8 kHz

fBCLK = 32 fLRCLK

fSCKI = 768 fLRCLK = 6.144 MHz

MSR[2:0] = 110 and NPR[5:0] = 000000

Changing MSR value has no effect. Changing NPR value results in shape distortion of the sine (only 000000 value gives correct signal).

I have also tried to clock the codec with fSCKI = 256 fLRCLK = 2.048 MHz and it works correctly.

The question is: why doesn't it work correctly with fLRCLK = 8 kHz and fSCKI = 1536 fLRCLK = 12.288 MHz in I2S SLAVE mode? What am I missing?