Please let me know about PBTL MODE

My Customer use PBTL for TAS5508C_ TAS5631B, but in trouble in ES set now, )... please let me know...

Q1

When does TAS5631B latch the Mode status (M3=M1=0, M2=1) ?

Is it on the start up at GVDD(=12V) ? or start up at PVDD?

My customer set PVDD first, then M3/M2/M1 set, then set GVDD.

We are concerned about it may be cause any problem.

Please let me know the timing of M3/M2/M1 latching for mode selection.

Q2

Data sheet Page 6 TYPICAL Block Diagram says M3/M2/M1 should be set by Hard wire mode control

That is to say, to control M3~M1, any I/O expander i.e.,TCA6408 's output is not recommended for changing the mode from BTL/PBTL?

My client 's power up sequence is I/O expander is setting M3~M1 for 1/0/1 first and then GVDD is set...

Q3

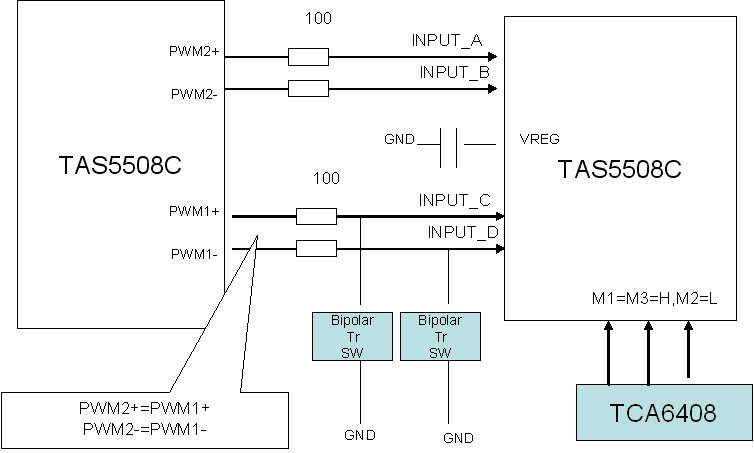

In case PBTL, we know we should set INPUT_C=VREG (Or GND), INPUT_D=GND. ( Data sheet page3 and page 17)

But my customer ties TAS5508 PWM1+ with INPUT_C and GND( thru switch) together ( wired Oring).

Please see attached jpg. ( PWM1-and INPUT_D is same manner.)

Also, TAS5508B PWM1+=PWM2+, PWM1-=PWM2-,

Is this not -recommended?

Or , is it OK because TAS5631 neglects INPUT_C & D if PBTL mode.

If it is not recommended, what kind of the problem may occur?

Please kindly refer to attached.

My customer is just in hurry for ES evaluating and then Pilot run CAD out date is soon.

Please let us know in 1~2days/

Best Regards