Hi,TIer.

I use PCM1865 to capture FOUR channel mono audio to TI's soc dm8168 via TDM mode, and pcm1865 acts as master.

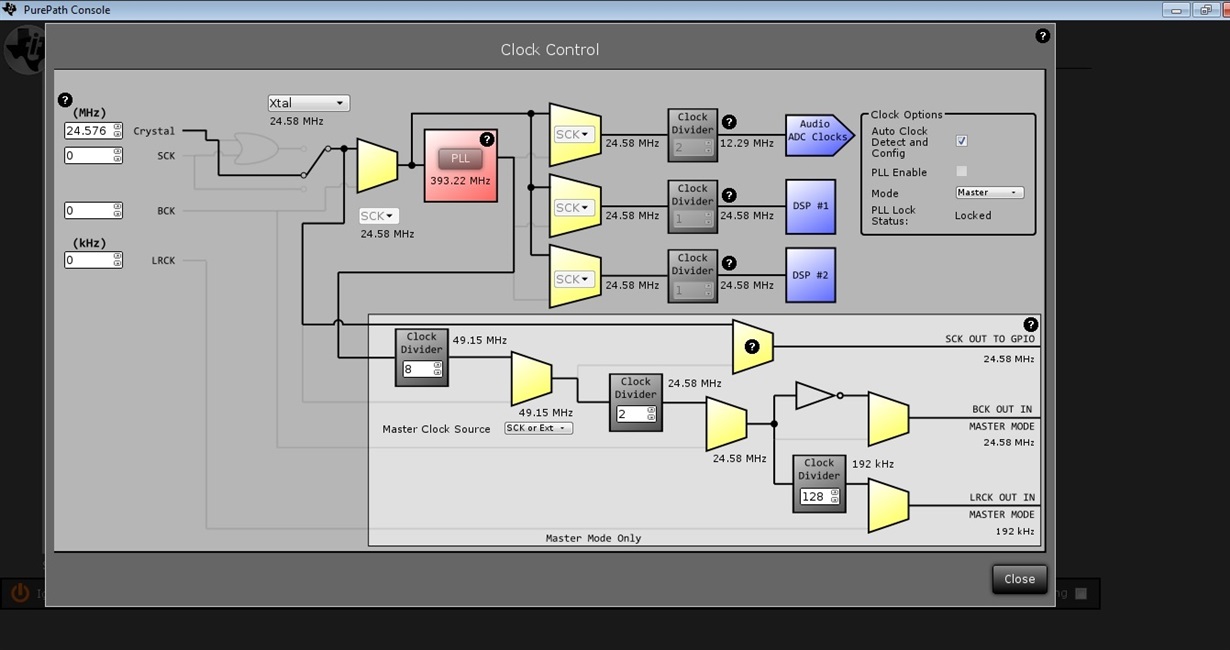

I use our DM8168 custom board and PCM1865 EVM to test. I install a 24.575M osc into the PCM1865 EVM.

And wired the +5V,GND,SCL,SDA from our 8168 board to PCM1865 EVM.

After Power on the 8168 board and PCM1865 EVM.

I write the following data to 1865's register, and I2C write operation is successful for I have read back the corresponding register.(All operation is on page0)

--------------------------------------------------------

data register

0x1f 0x0b //16bit PCM, TDM/DSP mode,1/256 duty cycle of LRCK.

0x10 0x20 //Master,without auto clock detect.Use

0x01 0x21 //DSP1 divider:1/2 12.288M

0x01 0x22 //DSP2 divider:1/2 12.288M

0x03 0x23 //ADC clock divier:1/4 6.144M

0x01 0x26 //SCK to BCK:1/2 12.288M 256FS

0xff 0x27 //BCK to LRCK:1/256 48K sample rate

0x00 0x28 //disable PLL

--------------------------------------------------------

I do NOT use PLL. And test in 48K sample rate.

I have checked the status register, power,clock,etc.There is no error.

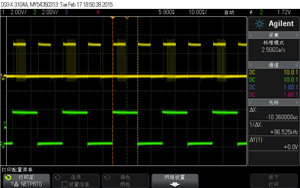

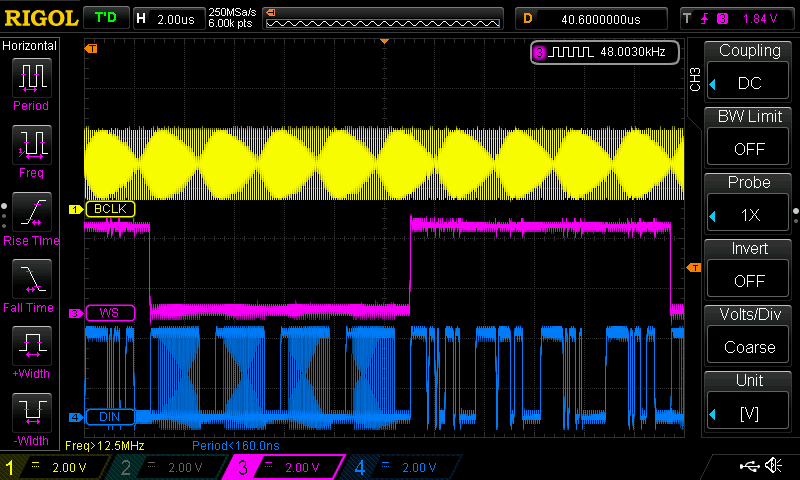

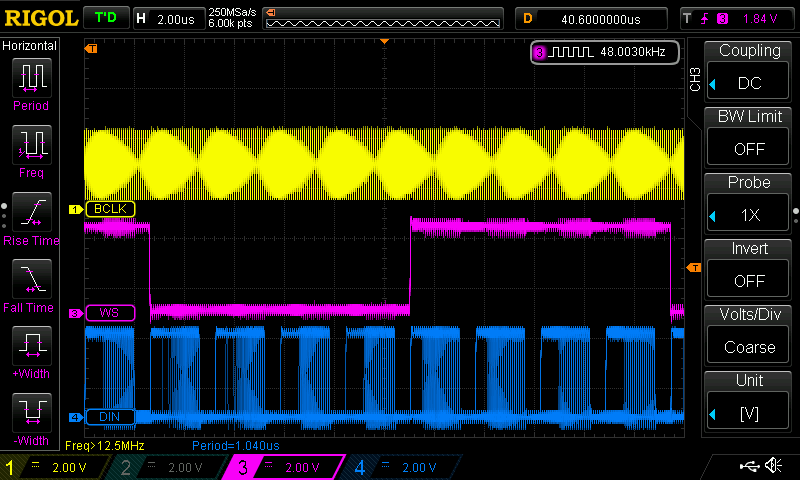

And I have measured the frequency of LRCK, and BCK. BCK is 12.288M.LRCK is 48K. But according to the spec, in TDM mode,the duty cyclone should be 1/256.But when I measured, it is still 50% duty cycle.What may cause it?

And there is no OUTPUT on DOUT pin.

Expecting for any reply.

BR!