Dear Expert,

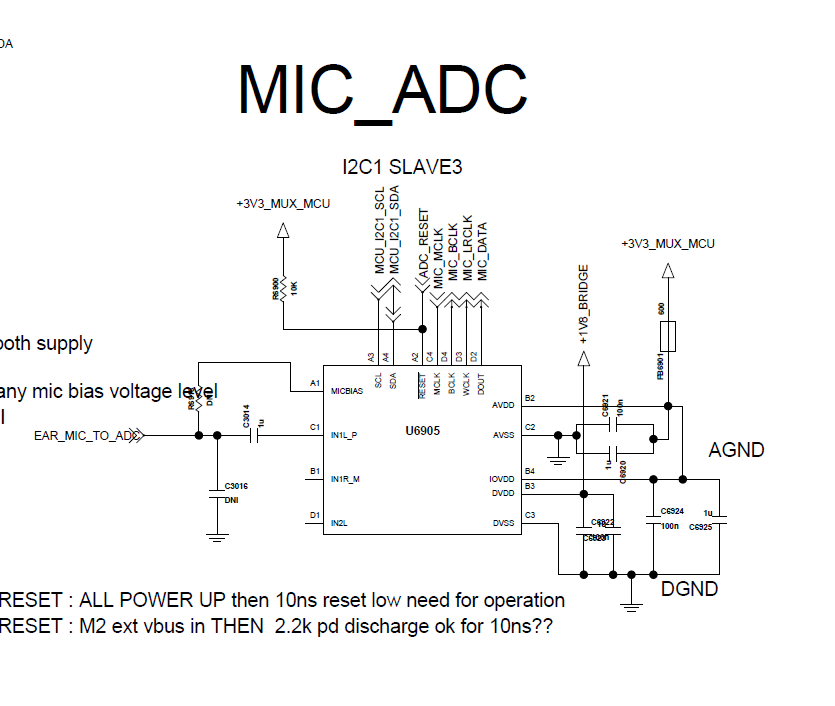

My customer is drawing schematice with TLV320ADC3001.

BCLK from external device is 48kHz or 44.1kHz, but there's no MCLK.

Is it possible TLV320ADC3001 to work with the 48kHz BCLK?

Here's question for proper schematic.

1. How to terminate MCLK pin of TLV320ADC3001?

2. I want fS to be 48kHz as same as BCLK from external device. Can I set all other parameters to one as below?

PLLCLK_IN=BCLK=48kHz, K=R=NADC=MADC=AOSR=P=1

fS = (PLLCLK_IN × K × R) / (NADC × MADC × AOSR × P)

Thank you in advance.