Hi,

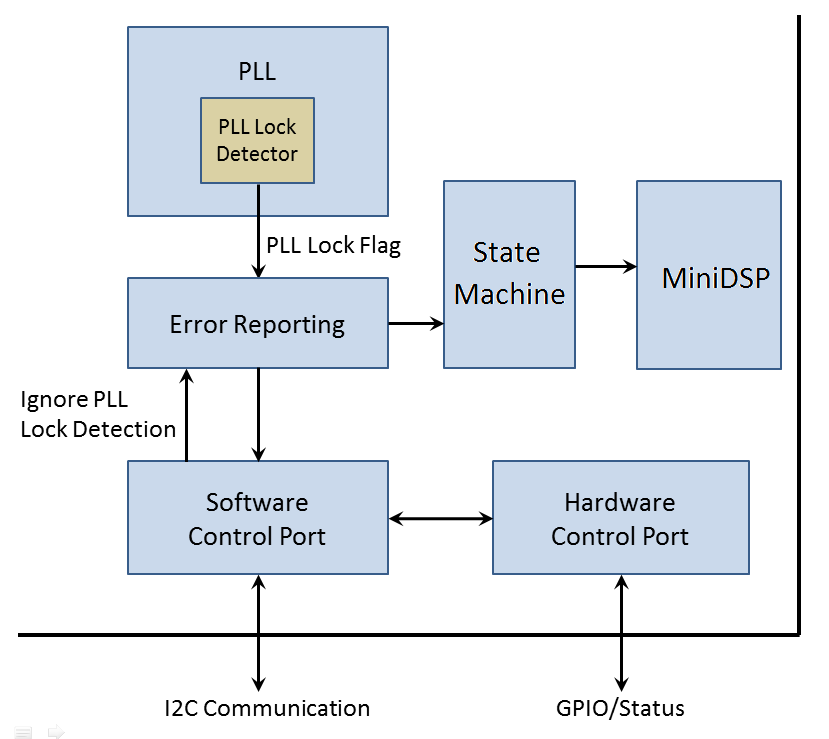

The sound quality is degraded if setting the bit for "Ignore PLL Lock Detection [0]" to "1"(the pll unlocks are ignored) in P0-R37.

So, could you please tell us the difference between the internal processing if ignoring this function or not ?

For instance, does the lock range of the pll change by this setting ?

Best regards,

Kato