Hi

I am using this chip for connecting to a TX1 module from nvidia

The chip is connected to the processor through the I2S and I2C interfaces

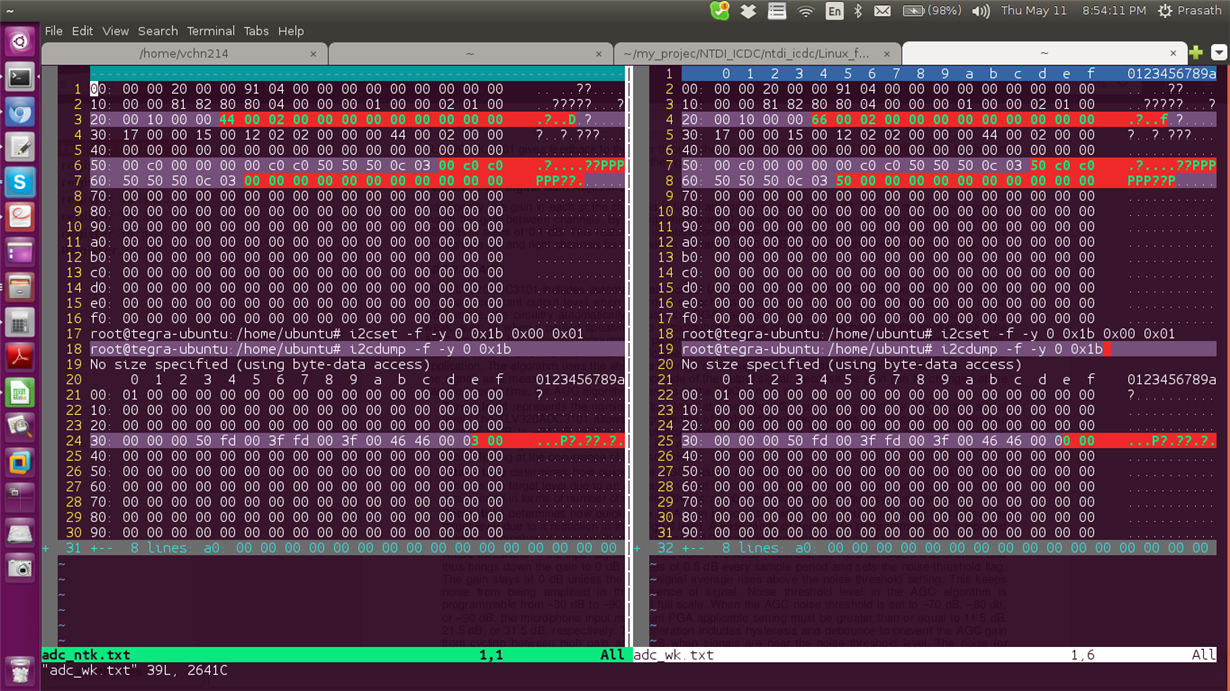

I am able to write the configuration to the Device configured in I2S slave mode

I have given BCLK MCLK and WCLK for the chip from the processor

BCLK----------2.822 MHZ

MCLK----------11.286MHZ

WCLK----------44.1KHZ

In the reference board the chip is configured in I2S slave mode

we are getting the same values of clock from the micro controller in reference board

But we are not able to find any activity in our board in Dout Pin. whereas in reference board there is activity in the Dout pin

What are the possible checks can be done for debugging this