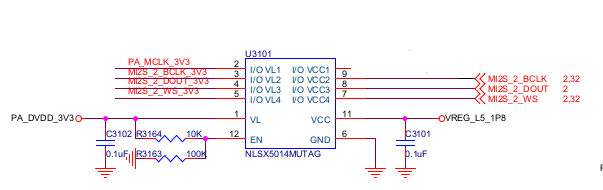

1:TAS5756 is slave mode as 3-wire PCM mode. There is not mclk, just connect blck and lrclk in my hardware principle chart like below:

I'd like add that, Bclk is 1.536MHZ, LRclk is 48KHZ, FORMAT is 16bit .

2: As note in 8.3.3.4, I disable auto set mode with Page0-R37 bit 1 and ignored MCLK, configure the register R37 value is 0x12;

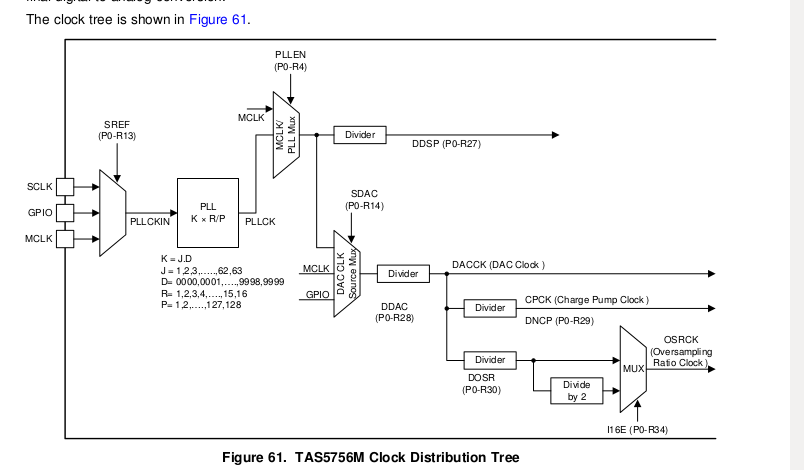

Like 8.3.3.4 introduce: I should configure below:

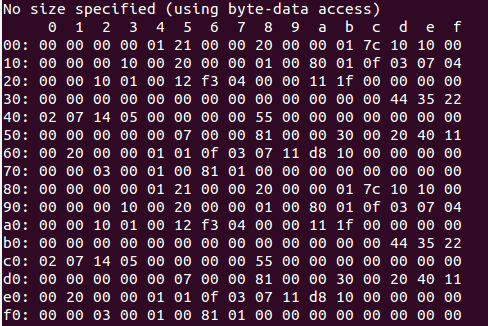

3: My register configure is like below:

Page0:

1: R4—— 0x00 (disable PLL)

2: R37—— 0x12 (ignored MCLK err report and disable auto set mode)

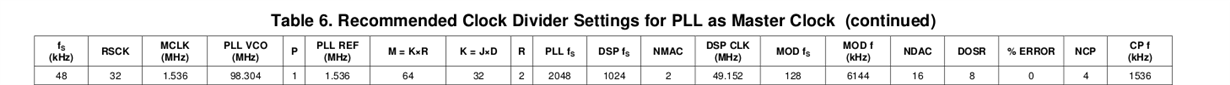

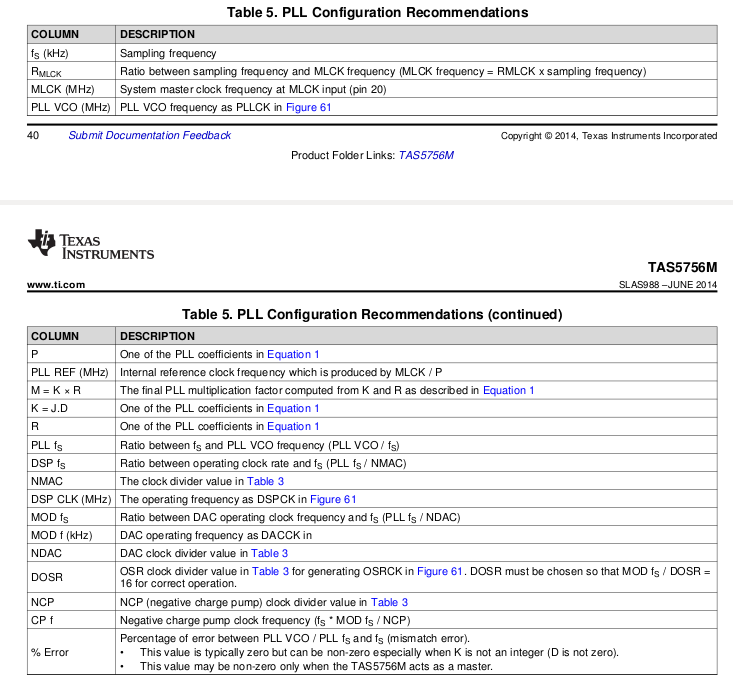

3: R13—— 0x10 (PLL reference clock is bclk)

4: R20—— 0x0 (P ==1)

5: R21—— 0x20 (J ==32)

6: R22—— 0x0 ( D==0)

7: R23—— 0x0 ( D==0)

8: R24—— 0x1 (R==2)

9: R4 —— 0x01(enable PLL)

10: R14—— 0x10 (DAC clock source is PLL)

11: R27—— 0x1 (DSP clock divide)

12: R28—— 0xf (DAC clock divide)

13: R29—— 0x3 (CP clock divide)

14: R30—— 0x7 (OSR clock divide)

15: R34—— 0x10 This bit enables or disables the 16x interpolation mode.(I donnot know what this bit mean? Can you help me?)

4: But so sorry, there is no sound. Thank you for review my configure, if there are any error?