Hi all,

In a design I'm working on I need to connect two devices over I2S. Obviously one has data input and the other data output, but, unlike many other devices (especially the receiver), both devices want to be the I2S clock master.

I can not change this. It would be a lot easier if I could, I know, but it can not be done.

So, I have to connect two I2S clock masters to each other.

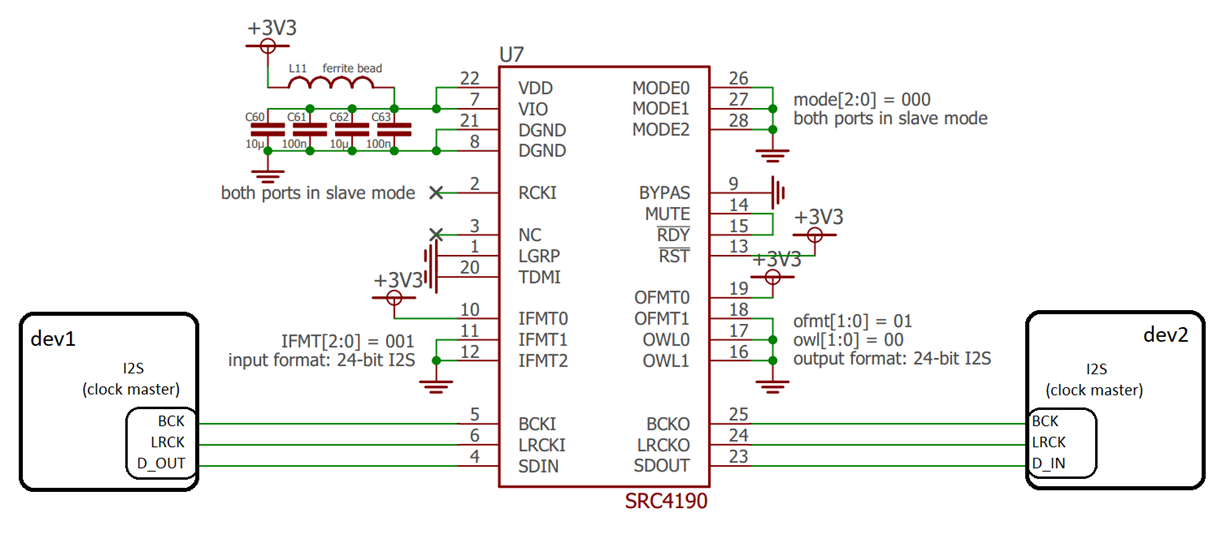

What I've come up with, and I honestly know no other option, is to make use of an asynchronous sample rate converster (ASRC). I choose the SRC4190 from TI in the design and configured it as I2S slave input and I2S slave output so I can hookup two I2S masters.

It's a hardwired configuration, see my setup below:

According to the datasheet, this should work. I see no reason why it would not.

However, we have just build an actual prototype of the whole design and this ASRC seems not to work.

I've measured the SRC I2S input (pin5, 6, 4) and this is fine.

Also, the same I2S signals are going to another device elsewhere in the design and there is no problem, so I'm sure the I2S is appearing valid at the SRC input.

At the SRC I2S output (SDOUT, pin 23) I measure nothing however, it just stays low.

Can anyone please validate the design above?

A TI-engineer already told me this would work fine when I asked this in another (sub)tread on the Audio Amplifier forum. However without showing this schematic.

What else can be causing this? Have I set the configuration wrong?

I really don't understand.

Thanks in advance!

Kind regards!