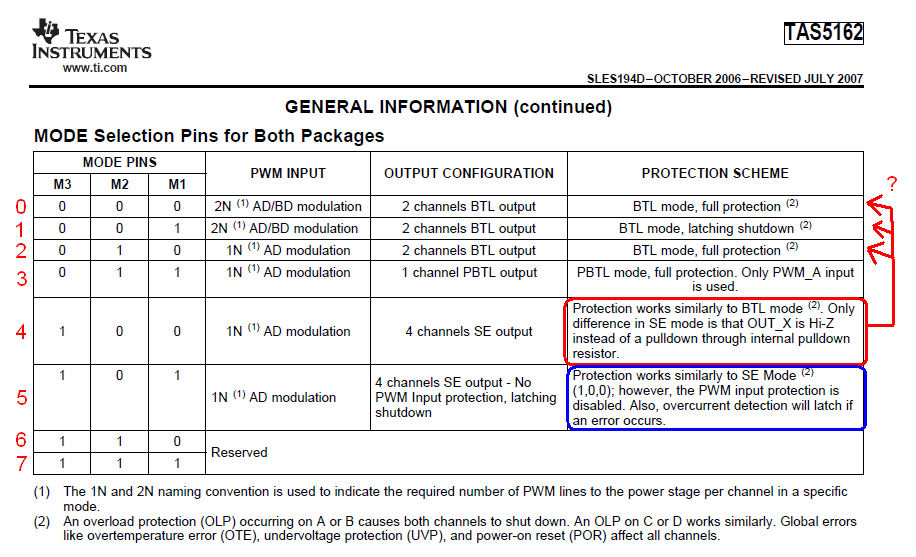

We are working on a upper segment class D audio amplifier and selected TAS5162 as the output stage. After studying the datasheet we have a few questions

Question 1. Box marked in red on the attached picture. Mode 4 says:

Protection works similarly to BTL mode.

But which BTL mode? Because there are 3 BTL modes, and they have different protections.

Mode 0 and 2 have full protection, and mode 1 has latching protection. Do mode 4 have full protection as modes 2/0, or have latching protection as mode 1?

Question 2: Box marked in blue on the attached picture.

the PWM input protection is disabled.

Does it mean that PWM duty cycle is not monitored and there are no automatic protection mechanisms ? So is it possible to use for example 99% duty cycle instead of 97.1% (of course in situation where High Side powering are provided in other way than bootstraping, for example using isolated DC/DC converters)?

Question 3. What does full protection and latching protection mean ? Is it, to understand it in more precisely, probing protection and latching protection? By probing we mean auto restarting from overcurrent, for example in periods of 1 second. And do we understand correctly that latching is permanent, so manual reset is required ?

Question 4. Are we right that the only difference between mode 0 and mode 4 is that in the SE mode OUT_X is Hi-Z instead of a pulldown through internal pulldown resistor ?

And we are aware that Mode 0, although it is a BTL stereo mode, has independent 4 PWM inputs. So it may be possible to drive PWMs independently, creating 4 SE outputs. We don't see any information that Mode 0 or 1 checks if PWM inputs is in antiphase (A = B+180, and C = D+180) ?

Question 5. Is the protection reaction automatically executed on all pairs A/B and C/D in all modes? For example in mode 4 (4 independent SE outputs) if overcurrent occurs in output A, does output B also shut down?

Question 6. There is one SD output, are we right then that it is not possible to check what PWM signal pair has shut down ? And is it necessary to reset all outputs (using RESET_AB and RESERT_CD) in all overcurrent situations ?

Regards, Pawel