Other Parts Discussed in Thread: TAS2562

Hi Sirs,

Sorry to bother you.

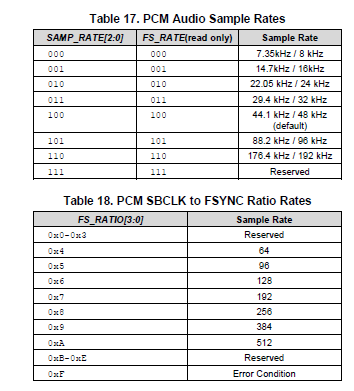

We would like to know does TAS2552 support Ratio Rates of 32?

If not does TI have others solution can suggest it?

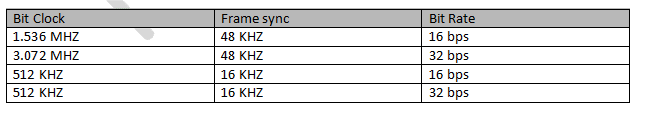

Because our table shown for SBCLK to FSYNC ratios,

1.1.536M/48K = 32

2. 3.072M/48k = 64

3.512k/16k = 32

But from datasheet didn't show support Ratio Rates of 32.