Hello

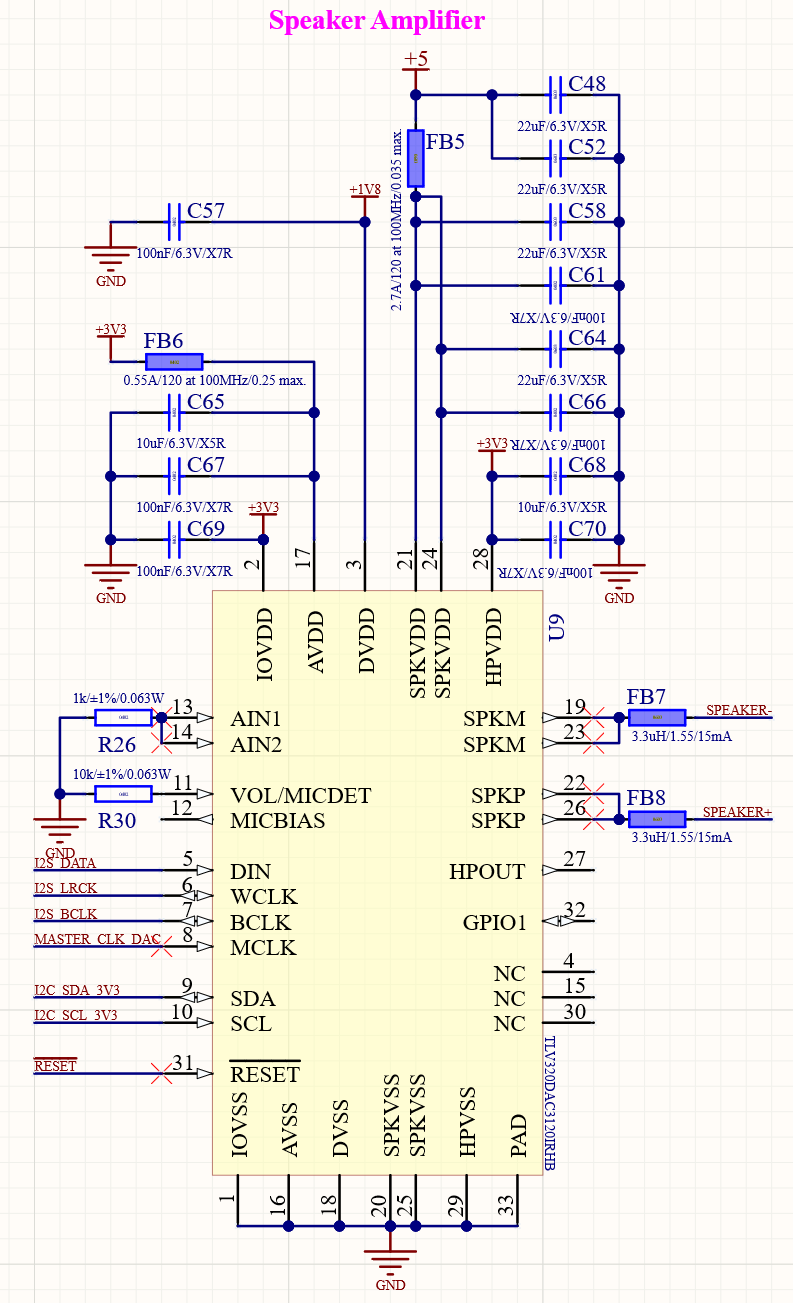

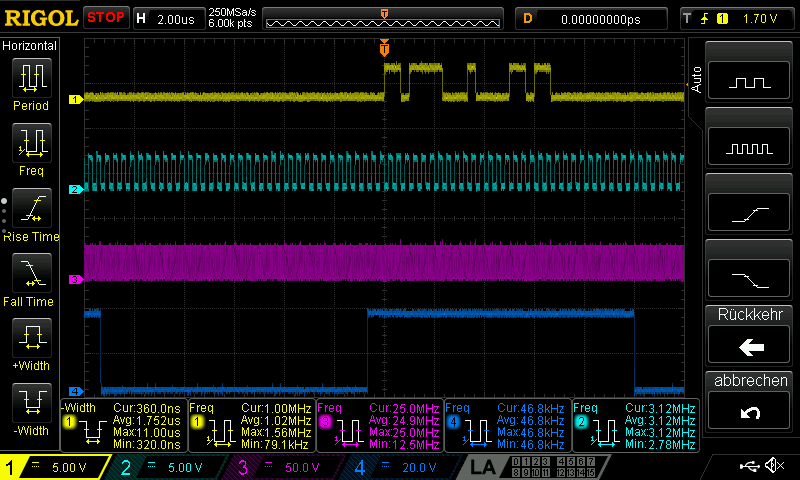

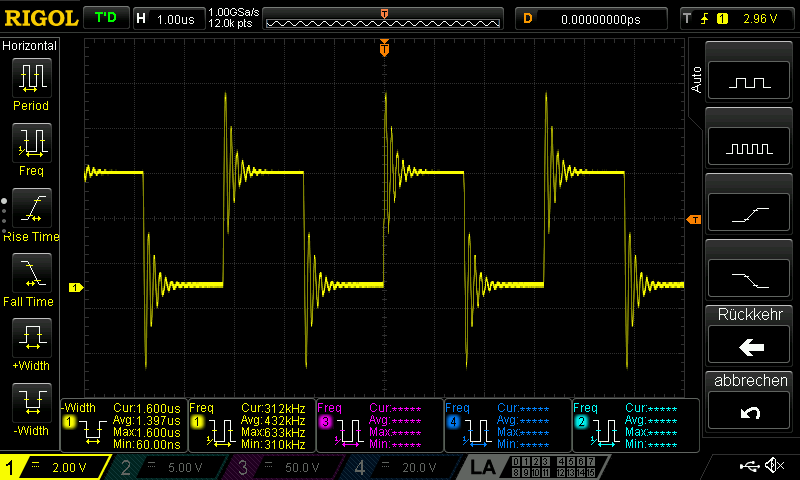

i'm using the TI TLV320DAC3120 and the XMOS XVF3100. The i2c communication works but i'm not getting anything out of the ti to a speaker like with the dev board TI ACEV-1B. I guess i have to set up the clocks... The WCLK is 15.6 kHz, the BCLK is 1 MHz and the MCLK is 24 MHz. What do i have to set up and how to calculate the correct values?

The output from xmos is through i2s and do i have to set up there anything in the ti ?

Thanks in advance

twittich