Hello. TLV320AIC3110 has a lot of settings and I'm confused. Also, SAI in STM32 has much more settings than just I2S, I don’t understand how to make these two things work together.

I do not understand what to specify in the FrameInit and SlotInit structure. Here is my STM32 code:

hsai_BlockA2.Instance = SAI2_Block_A; hsai_BlockA2.Init.Protocol = SAI_FREE_PROTOCOL; hsai_BlockA2.Init.AudioMode = SAI_MODEMASTER_TX; hsai_BlockA2.Init.DataSize = SAI_DATASIZE_16; // -- hsai_BlockA2.Init.FirstBit = SAI_FIRSTBIT_MSB; hsai_BlockA2.Init.ClockStrobing = SAI_CLOCKSTROBING_FALLINGEDGE; hsai_BlockA2.Init.Synchro = SAI_ASYNCHRONOUS; hsai_BlockA2.Init.OutputDrive = SAI_OUTPUTDRIVE_ENABLE; hsai_BlockA2.Init.NoDivider = SAI_MASTERDIVIDER_ENABLE; hsai_BlockA2.Init.FIFOThreshold = SAI_FIFOTHRESHOLD_1QF; hsai_BlockA2.Init.AudioFrequency = SAI_AUDIO_FREQUENCY_48K; hsai_BlockA2.Init.SynchroExt = SAI_SYNCEXT_DISABLE; hsai_BlockA2.Init.MonoStereoMode = SAI_STEREOMODE; hsai_BlockA2.Init.CompandingMode = SAI_NOCOMPANDING; hsai_BlockA2.Init.TriState = SAI_OUTPUT_NOTRELEASED; hsai_BlockA2.FrameInit.FrameLength = 64; // -- hsai_BlockA2.FrameInit.ActiveFrameLength = 32; // -- hsai_BlockA2.FrameInit.FSDefinition = SAI_FS_CHANNEL_IDENTIFICATION; // -- hsai_BlockA2.FrameInit.FSPolarity = SAI_FS_ACTIVE_LOW; // -- hsai_BlockA2.FrameInit.FSOffset = SAI_FS_BEFOREFIRSTBIT; // -- hsai_BlockA2.SlotInit.FirstBitOffset = 0; hsai_BlockA2.SlotInit.SlotSize = SAI_SLOTSIZE_DATASIZE; hsai_BlockA2.SlotInit.SlotNumber = 2; hsai_BlockA2.SlotInit.SlotActive = SAI_SLOTACTIVE_0 | SAI_SLOTACTIVE_1;

Also, I got confused with TLV320AIC3110, I need:

1) Get MIC1PL in my I2S (SAI)

2) The data that I send from STM32 to TLV on I2S is reproduced in SPR / SPL

My registers:

Page 0:

reg[0] 0 reg[1] 0 reg[2] 1 reg[3] 86 reg[4] 0 reg[5] 17 reg[6] 5 reg[7] 4 reg[8] 176 reg[9] 0 reg[10] 0 reg[11] 4 reg[12] 2 reg[13] 0 reg[14] 128 reg[15] 128 reg[16] 8 reg[17] 0 reg[18] 132 reg[19] 132 reg[20] 48 reg[21] 128 reg[22] 4 reg[23] 0 reg[24] 0 reg[25] 0 reg[26] 1 reg[27] 0 reg[28] 0 reg[29] 0 reg[30] 1 reg[31] 0 reg[32] 0 reg[33] 0 reg[34] 0 reg[35] 0 reg[36] 192 reg[37] 136 reg[38] 0 reg[39] 0 reg[40] 0 reg[41] 0 reg[42] 0 reg[43] 0 reg[44] 0 reg[45] 0 reg[46] 0 reg[47] 0 reg[48] 0 reg[49] 0 reg[50] 0 reg[51] 2 reg[52] 50 reg[53] 18 reg[54] 2 reg[55] 2 reg[56] 2 reg[57] 17 reg[58] 16 reg[59] 0 reg[60] 1 reg[61] 4 reg[62] 0 reg[63] 214 reg[64] 12 reg[65] 0 reg[66] 0 reg[67] 0 reg[68] 111 reg[69] 56 reg[70] 0 reg[71] 0 reg[72] 0 reg[73] 0 reg[74] 0 reg[75] 238 reg[76] 16 reg[77] 216 reg[78] 126 reg[79] 227 reg[80] 0 reg[81] 128 reg[82] 0 reg[83] 24 reg[84] 0 reg[85] 0 reg[86] 0 reg[87] 0 reg[88] 127 reg[89] 0 reg[90] 0 reg[91] 0 reg[92] 0 reg[93] 0 reg[94] 0 reg[95] 0 reg[96] 0 reg[97] 0 reg[98] 0 reg[99] 0 reg[100] 0 reg[101] 0 reg[102] 0 reg[103] 0 reg[104] 0 reg[105] 0 reg[106] 0 reg[107] 0 reg[108] 0 reg[109] 0 reg[110] 0 reg[111] 0 reg[112] 0 reg[113] 0 reg[114] 0 reg[115] 0 reg[116] 0 reg[117] 0 reg[118] 0 reg[119] 0 reg[120] 0 reg[121] 0 reg[122] 0 reg[123] 0 reg[124] 0 reg[125] 0 reg[126] 0 reg[127] 0

Page 1:

reg[0] 1 reg[1] 0 reg[2] 0 reg[3] 0 reg[4] 0 reg[5] 0 reg[6] 0 reg[7] 0 reg[8] 0 reg[9] 0 reg[10] 0 reg[11] 0 reg[12] 0 reg[13] 0 reg[14] 0 reg[15] 0 reg[16] 0 reg[17] 0 reg[18] 0 reg[19] 0 reg[20] 0 reg[21] 0 reg[22] 0 reg[23] 0 reg[24] 0 reg[25] 0 reg[26] 0 reg[27] 0 reg[28] 0 reg[29] 0 reg[30] 0 reg[31] 4 reg[32] 6 reg[33] 62 reg[34] 0 reg[35] 0 reg[36] 127 reg[37] 127 reg[38] 127 reg[39] 127 reg[40] 2 reg[41] 2 reg[42] 0 reg[43] 0 reg[44] 32 reg[45] 134 reg[46] 9 reg[47] 0 reg[48] 32 reg[49] 64 reg[50] 0 reg[51] 0 reg[52] 0 reg[53] 0 reg[54] 0 reg[55] 0 reg[56] 0 reg[57] 0 reg[58] 0 reg[59] 0 reg[60] 0 reg[61] 0 reg[62] 0 reg[63] 0 reg[64] 0 reg[65] 0 reg[66] 0 reg[67] 0 reg[68] 0 reg[69] 0 reg[70] 0 reg[71] 0 reg[72] 0 reg[73] 0 reg[74] 0 reg[75] 0 reg[76] 0 reg[77] 0 reg[78] 0 reg[79] 0 reg[80] 0 reg[81] 0 reg[82] 0 reg[83] 0 reg[84] 0 reg[85] 0 reg[86] 0 reg[87] 0 reg[88] 0 reg[89] 0 reg[90] 0 reg[91] 0 reg[92] 0 reg[93] 0 reg[94] 0 reg[95] 0 reg[96] 0 reg[97] 0 reg[98] 0 reg[99] 0 reg[100] 0 reg[101] 0 reg[102] 0 reg[103] 0 reg[104] 0 reg[105] 0 reg[106] 0 reg[107] 0 reg[108] 0 reg[109] 0 reg[110] 0 reg[111] 0 reg[112] 0 reg[113] 0 reg[114] 0 reg[115] 0 reg[116] 0 reg[117] 0 reg[118] 0 reg[119] 0 reg[120] 0 reg[121] 0 reg[122] 0 reg[123] 0 reg[124] 0 reg[125] 0 reg[126] 0 reg[127] 0

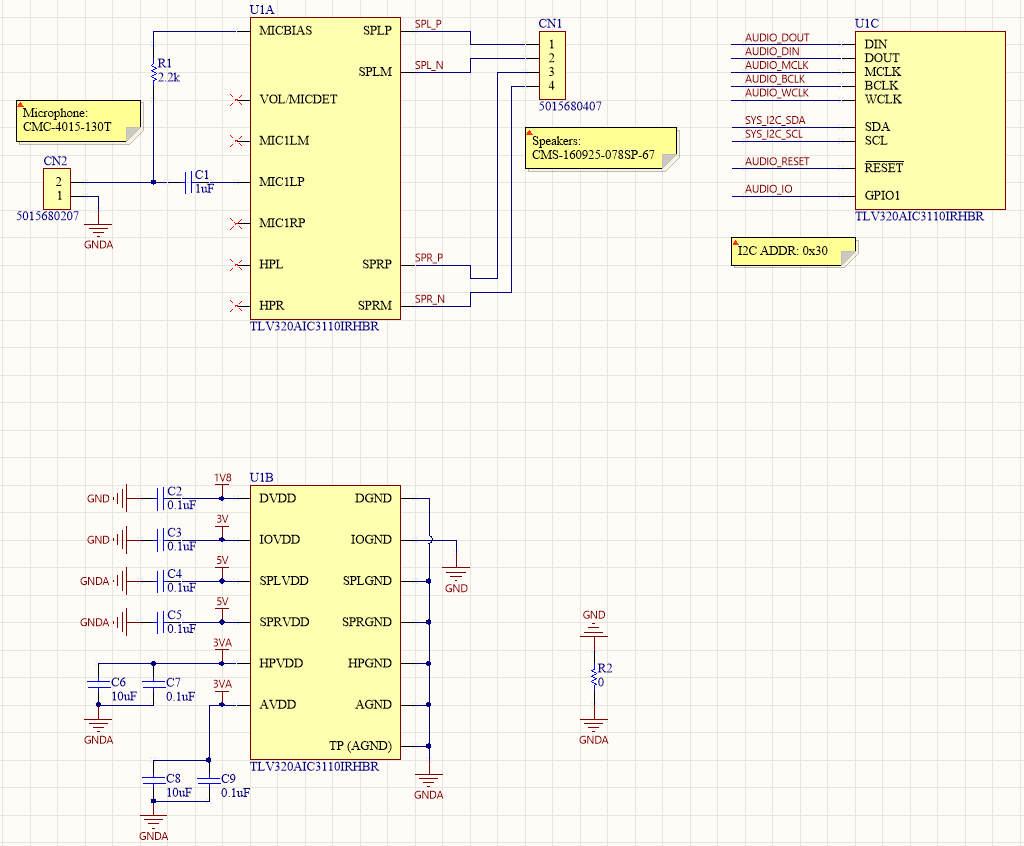

My scheme: