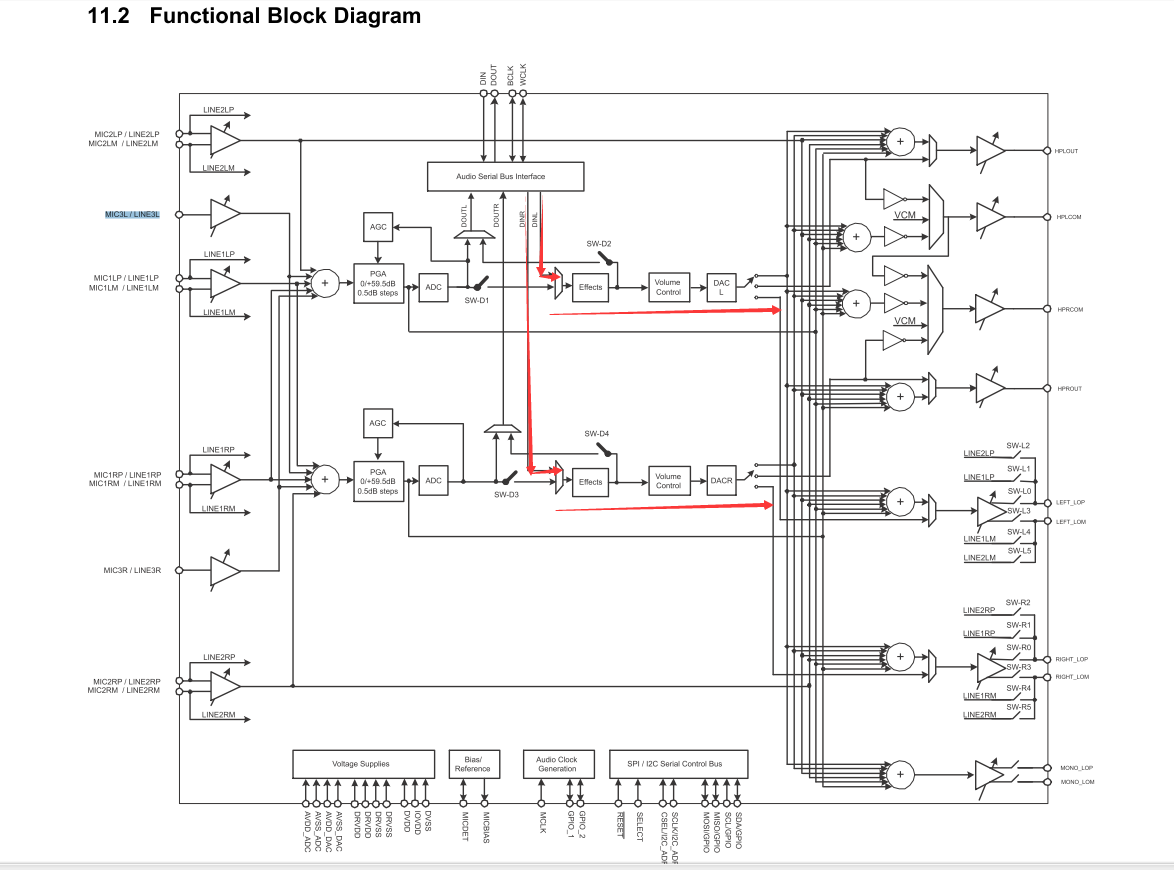

external i2s,MCLK=12MHZ,WCLK=48KHZ,BLCK has audio data input with Oscilloscope,, but LEFT/RIGHT_LOUT Can't produce sound,why? thanks!

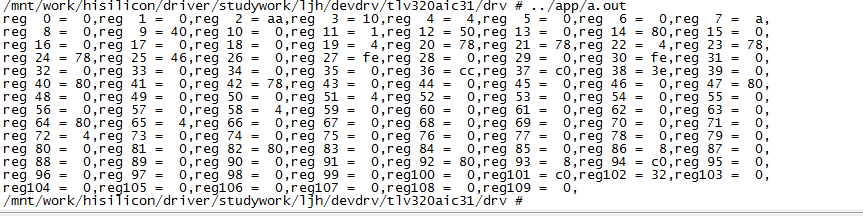

this is 3106 registers value

tlv320aic31_write(IIC_device_addr[chip_num], 7, 0xa);/* FSref = 48 kHz */

/*left and right DAC power on*/ || soft_reset

tlv320aic31_write(IIC_device_addr[chip_num], 37, 0xc0);

/*left DAC not muted*/

tlv320aic31_write(IIC_device_addr[chip_num], 43, 0x0);

/*right DAC not muted*/ ~

tlv320aic31_write(IIC_device_addr[chip_num], 44, 0x0);

//left-dac

tlv320aic31_write(IIC_device_addr[chip_num], 82, 0x80);

tlv320aic31_write(IIC_device_addr[chip_num], 86, 0x08);

//right-dac

tlv320aic31_write(IIC_device_addr[chip_num], 92, 0x80);

tlv320aic31_write(IIC_device_addr[chip_num], 93, 0x08);